# SD Specifications Part A2 SD Host Controller Simplified Specification

Version 4.20

**April 10, 2017**

Technical Committee SD Association

**Revision History**

| Date              | Version | Changes compared to previous issue                                                                                              |  |  |  |  |

|-------------------|---------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| April 3, 2006     | 1.00    | Host Controller Simplified Specification Version 1.00                                                                           |  |  |  |  |

| February 8, 2007  | 2.00    | Host Controller Simplified Specification Version 2.00                                                                           |  |  |  |  |

| February 25, 2011 | 3.00    | Host Controller Simplified Specification Version 3.00 (1) UHS-I Support (2) Shared Bus Support                                  |  |  |  |  |

| April 10, 2017    | 4.20    | Host Controller Simplified Specification Version 4.20 (1) UHS-II Support (2) ADMA3 Support (3) 64-bit System Addressing Support |  |  |  |  |

To the extent this proposed specification, which is being submitted for review under the IP Policy, implements, incorporates by reference or refers to any portion of versions 1.0 or 1.01 of the SD Specifications (including Parts 1 through 4), adoption of the proposed specification shall require Members utilizing the adopted specification to obtain the appropriate licenses from the SD-3C, LLC, as required for the utilization of those portion(s) of versions 1.0 or 1.01 of the SD Specifications.

For example, implementation of the SD Specifications in a host device under versions 1.0 or 1.01 and under the adopted specification requires the execution of an SD Host Ancillary License Agreement with the SD-3C, LLC; and implementation of the SD Specifications under versions 1.0 or 1.01 and under the proposed specification in an SD Card containing any memory storage capability (other than for storage of executable code for a controller or microprocessor within the SD Card) requires the execution of an SD Memory Card License Agreement with the SD-3C, LLC.

# Release of SD Simplified Specification/Addendum

The following conditions apply to the release of the SD Simplified Specification/Addendum by the SD Card Association. The Simplified Specification/Addendum is a subset of the complete version of SD Specification/Addendum that is owned by the SD Card Association.

# **Conditions for publication**

## **Publisher and Copyright Holder:**

SD Card Association 2400 Camino Ramon, Suite 375 San Ramon, CA 94583 USA Telephone: +1 (925) 275-6615,

Fax: +1 (925) 886-4870 E-mail: office@sdcard.org

#### Notes:

This Simplified Specification/Addendum is provided on a non-confidential basis subject to the disclaimers below. Any implementation of the Simplified Specification/Addendum may require a license from the SD Card Association or other third parties.

#### **Disclaimers:**

The information contained in the Simplified Specification/Addendum is presented only as a standard Specification/Addendum for SD Cards and SD Host/Ancillary products and is provided "AS-IS" without any representations or warranties of any kind. No responsibility is assumed by the SD Card Association for any damages, any infringements of patents or other right of the SD Card Association or any third parties, which may result from its use. No license is granted by implication, estoppel or otherwise under any patent or other rights of the SD Card Association or any third party. Nothing herein shall be construed as an obligation by the SD Card Association to disclose or distribute any technical information, know-how or other confidential information to any third party.

#### Conventions Used in This Document

#### **Naming Conventions**

- Register names are shown in italic text such as *Present State*.

- Names of bits or fields within registers are in bold text such as **Buffer Write Enable**.

- Signal names are capitalized, bold and italic, followed by '#' if low active such as SDCD#.

- Some terms are capitalized to distinguish their definition from their common English meaning. Words not capitalized have their common English meaning.

- Register names and the names of fields and bits in registers and headers are presented with the first letter capitalized and the remainder in lower case.

#### **Numbers and Number Bases**

- Hexadecimal numbers are written with a lower case "h" suffix, e.g., FFFFh and 80h.

- Binary numbers are written with a lower case "b" suffix (e.g., 10b).

- Binary numbers larger than four digits are written with a space dividing each group of four digits, as in 1000 0101 0010b.

- All other numbers are decimal.

#### **Key Words**

- May: Indicates flexibility of choice with no implied recommendation or requirement.

- Shall: Indicates a mandatory requirement. Designers shall implement such mandatory requirements to ensure interchangeability and to claim conformance with the specification.

- Should: Indicates a strong recommendation but not a mandatory requirement. Designers should give strong consideration to such recommendations, but there is still a choice in implementation.

#### **Special Terms**

In this document, the following terms shall have special meaning:

• Host Controller Refers to an SD Host Controller that complies with this Specification.

Host Driver

Card Driver

Refers to the OS-specific driver for a Host Controller

Refers to a driver for an SD/SDIO card or card function

Host System (or System) Refers to the entire system, such as a cellular phone, containing the Host Controller

#### Implementation Notes

Some sections of this document provide guidance to Host Controller or Host Driver implementers. To distinguish non-mandatory guidance from other parts of the SD Host Specification, it will be shown as follows:

Implementation Note: This is an example of an implementation note.

# **Table of Contents**

| 1. Overview of the SD Standard Host                                 | 1  |

|---------------------------------------------------------------------|----|

| 1.1 Scope of the Standard SD Host                                   | 1  |

| 1.2 Register Map                                                    | 2  |

| 1.3 Multiple Slot Support                                           |    |

| 1.4 Supporting DMA                                                  |    |

|                                                                     |    |

| 1.5 SD Command Generation                                           |    |

| 1.5.2 UHS-II Mode Command Generation                                |    |

| 1.5.2.1 Command Issuing during CTS                                  |    |

| 1.5.2.2 Support of TID Check                                        |    |

| 1.6 Suspend and Resume Mechanism (Version 3.00 or less)             | 5  |

| 1.7 Buffer Control                                                  |    |

| 1.7.1 Control of Buffer Pointer (Non DMA)                           |    |

| 1.7.2 Determining Buffer Block Length                               |    |

|                                                                     |    |

| 1.8 Relationship between Interrupt Control Registers                |    |

| 1.9 HW Block Diagram and Timing Part                                | 11 |

| 1.10 Power State Definition of SD Host Controller                   | 12 |

| 1.11 Auto CMD12                                                     | 13 |

| 1.12 Controlling SDCLK                                              | 14 |

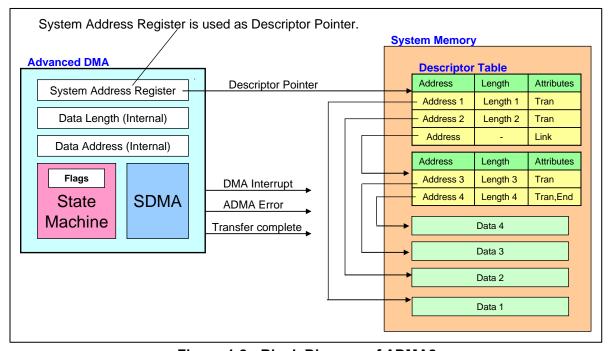

| 1.13 Advanced DMA                                                   | 15 |

| 1.13.1 ADMA Data Transfer between Host Controller and System Memory |    |

| 1.13.1.1 Block Diagram of ADMA2                                     |    |

| 1.13.1.2 An Example of ADMA2 Programming                            |    |

| 1.13.2 General Descriptor Table Format                              |    |

| 1.13.3 ADMA2                                                        |    |

| 1.13.3.1 ADMA2 Descriptor Format                                    |    |

| 1.13.3.2 ADMA2 States                                               |    |

| 1.13.3.3 Stop/Continue Function during ADMA2                        |    |

| 1.13.3.4 ADMA Error Status Register                                 |    |

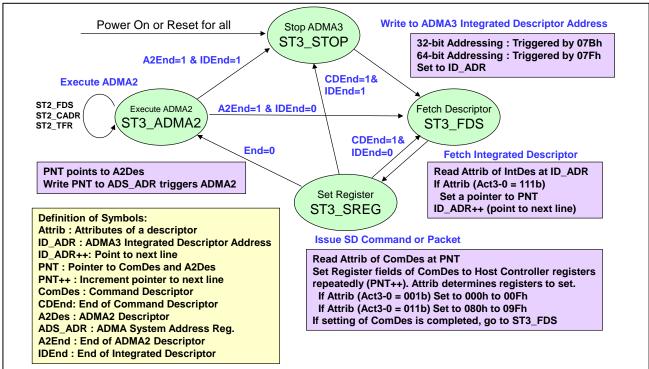

| 1.13.4.1 ADMA3 States                                               |    |

| 1.13.4.2 Command Descriptor Format                                  |    |

| 1.13.4.3 Integrated Descriptor Format                               |    |

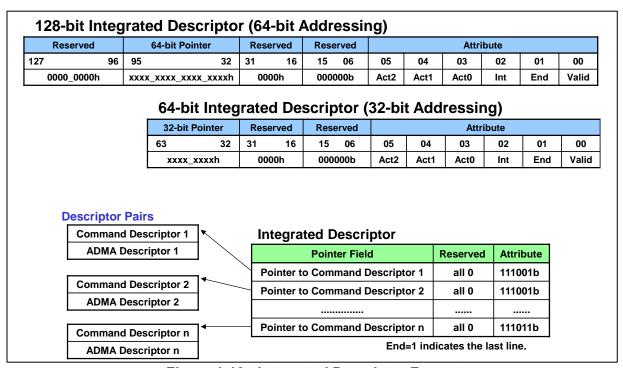

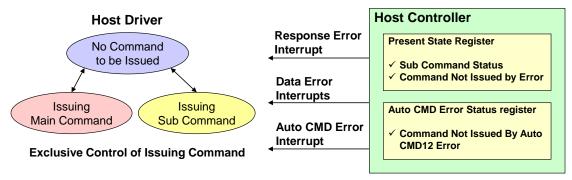

| 1.13.4.4 Response Error Check During ADMA3                          |    |

| 1.14 Test Registers                                                 | 27 |

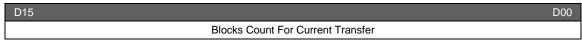

| 1.15 Block Count                                                    | 27 |

| 1.15.1 Selection of 16-bit or 32-bit Block Count                    |    |

| 1.15.2 Block Count for Auto CMD23                                   | 27 |

|                                                                     |    |

| 1.16 Sampling Clock Tuning                                          | 28 |

| 1.17 Command Issuing During Data Transfer                                     | 28    |

|-------------------------------------------------------------------------------|-------|

| 1.17.1 Response Error Check Function                                          | 28    |

| 1.17.2 Concept of How to Retry Command                                        |       |

| 1.17.3 Response Error Statuses                                                |       |

| 1.17.4 Summary of Command Issuing During Data Transfer                        | 31    |

| 2. SD Host Standard Register                                                  | 32    |

| 2.1 Summary of register set                                                   | 32    |

| 2.1.1 SD Host Control Register Map                                            |       |

| 2.1.2 Configuration Register Types                                            |       |

| 2.1.3 Register Initial Values                                                 |       |

| 2.1.4 Reserved Bits of Register                                               |       |

| 2.1.5 Register Categories                                                     |       |

| 2.2 Host Controller Interface Register                                        | 36    |

| 2.2.1 32-bit Block Count / (SDMA System Address) Register (Cat.A Offset 000h) | 36    |

| 2.2.2 Block Size Register (Cat.A Offset 004h)                                 |       |

| 2.2.3 16-bit Block Count Register (Cat.A Offset 006h)                         |       |

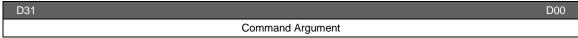

| 2.2.4 Argument Register (Cat.A Offset 008h)                                   |       |

| 2.2.5 Transfer Mode Register (Cat.A Offset 00Ch)                              |       |

| 2.2.6 Command Register (Cat.A Offset 00Eh)                                    |       |

| 2.2.7 Response Register (Cat.C Offset 010h)                                   |       |

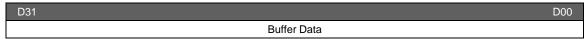

| 2.2.8 Buffer Data Port Register (Cat.C Offset 020h)                           |       |

| 2.2.9 Present State Register (Cat.C Offset 024h)                              |       |

| 2.2.11 Host Control 1 Register (Cat.C Offset 028h)                            |       |

| 2.2.12 Power Control Register (Cat.C Offset 029h)                             |       |

| 2.2.13 Block Gap Control Register (Cat.C Offset 02Ah)                         |       |

| 2.2.14 Wakeup Control Register (Cat.C Offset 02Bh)                            | 67    |

| 2.2.15 Clock Control Register (Cat.C Offset 02Ch)                             | 08    |

| 2.2.16 Timeout Control Register (Cat.A Offset 02Eh)                           | / 3   |

| 2.2.17 Software Reset Register (Cat.C Offset 02FH)                            |       |

| 2.2.19 Error Interrupt Status Register (Cat.C Offset 030h)                    | / 0   |

| 2.2.20 Normal Interrupt Status Enable Register (Cat.C Offset 034h)            | 02    |

| 2.2.21 Error Interrupt Status Enable Register (Cat.C Offset 0341)             | 00    |

| 2.2.22 Normal Interrupt Signal Enable Register (Cat.C Offset 038h)            |       |

| 2.2.23 Error Interrupt Signal Enable Register (Cat.C Offset 03Ah)             |       |

| 2.2.24 Auto CMD Error Status Register (Cat.A Offset 03Ch)                     |       |

| 2.2.25 Host Control 2 Register (Cat.C Offset 03Eh)                            | 96    |

| 2.2.26 Capabilities Register (Cat.C Offset 040h)                              |       |

| 2.2.27 Maximum Current Capabilities Register (Cat.C Offset 048h)              |       |

| 2.2.28 Force Event Register for Auto CMD Error Status (Cat.A Offset 050h)     |       |

| 2.2.29 Force Event Register for Error Interrupt Status (Cat.A Offset 052h)    |       |

| 2.2.30 ADMA Error Status Register (Cat.C Offset 054h)                         |       |

| 2.2.31 ADMA System Address Register (Cat.C Offset 05Fh-058h)                  | . 116 |

| 2.2.32 Preset Value Registers (Cat.C Offset 074-060h)                         | . 117 |

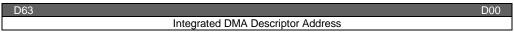

| 2.2.33 ADMA3 Integrated Descriptor Address (Cat.C Offset 07F-078h)            | . 119 |

| 2.3 UHS-II Registers in 000-0FFh                                              | .120  |

| 2.3.1 UHS-II Block Size (Cat.B Offset 081-080h)                               | .120  |

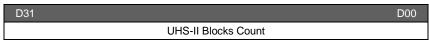

| 2.3.2 UHS-II Block Count (Offset 087-084h)                                    | .121  |

| 2.3.3 UHS-II Command Packet (Cat.B Offset 09B-088h)                           |       |

| 2.3.1 UHS-II Transfer Mode (Cat.B Offset 09D-09Ch)                            |       |

| 2.3.2 UHS-II Command (Cat.B Offset 09F-9Eh)                                   | .125  |

| 2.3.3 UHS-II Response (Cat.B Offset 0B3-0A0h)                       | 126 |

|---------------------------------------------------------------------|-----|

| 2.3.4 UHS-II MSG Select (Cat.B Offset 0B4h)                         |     |

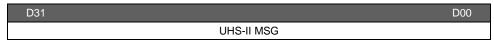

| 2.3.5 UHS-II MSG Register (Cat.B Offset 0BB-0B8h)                   |     |

| 2.3.6 UHS-II Device Interrupt Status (Cat.B Offset 0BD-0BCh)        |     |

| 2.3.7 UHS-II Device Select (Offset 0BEh)                            |     |

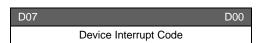

| 2.3.8 UHS-II Device Interrupt Code (Cat.B Offset 0BFh)              |     |

| 2.3.9 UHS-II Software Reset (Cat.B Offset 0C1-0C0h)                 |     |

| 2.3.10 UHS-II Timer Control (Cat.B Offset 0C3-0C2h)                 |     |

| 2.3.11 UHS-II Error Interrupt Status (Cat.B Offset 0C7-0C4h)        |     |

| 2.3.12 UHS-II Error Interrupt Status Enable (Cat.B Offset 0CB-0C8h) |     |

| 2.3.13 UHS-II Error Interrupt Signal Enable (Cat.B Offset 0CF-0CCh) |     |

| 2.3.14 Pointer Registers to mFFh-100h Area                          |     |

| 2.3.15 Slot Interrupt Status Register (Cat.C Offset 0FCh)           |     |

| 2.3.16 Host Controller Version Register (Cat.C Offset 0FEh)         | 138 |

| 2.4 UHS-II Registers in 100-1FFh                                    | 139 |

| 2.4.1 UHS-II Settings (Cat.B 16 Bytes)                              |     |

| 2.4.1.1 UHS-II General Settings (4 Bytes)                           |     |

| 2.4.1.2 UHS-II PHY Settings (4 Bytes)                               |     |

| 2.4.1.3 UHS-II LINK/TRAN Settings (8 Bytes)                         | 141 |

| 2.4.2 UHS-II Host Capabilities (Cat.B 16 Bytes)                     |     |

| 2.4.2.1 UHS-II General Capabilities (4 Bytes)                       |     |

| 2.4.2.2 UHS-II PHY Capabilities (4 Bytes)                           |     |

| 2.4.2.3 UHS-II LINK/TRAN Capabilities (8 Bytes)                     | 144 |

| 2.4.3 UHS-II Test Register (Cat.B 4 Bytes)                          |     |

| 2.4.3.1 Force Event for UHS-II Error Interrupt Status               | 146 |

| 2.4.4 Embedded Control Register (Cat.C 4 Bytes)                     | 148 |

| 3. SEQUENCE                                                         | 151 |

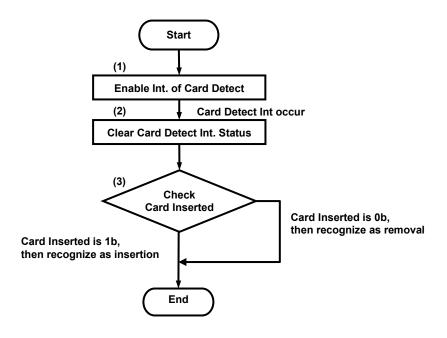

| 3.1 SD Card Detection                                               | 151 |

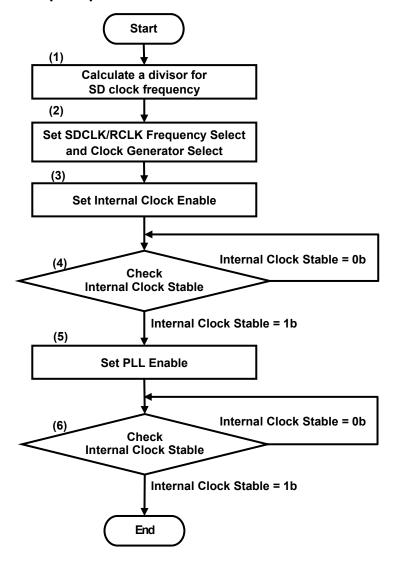

| 3.2 SD Clock Control                                                | 152 |

| 3.2.1 Internal Clock Setup Sequence                                 |     |

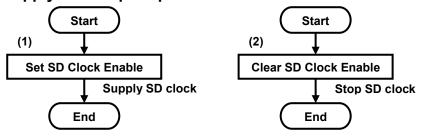

| 3.2.2 SD Clock Supply and Stop Sequence                             |     |

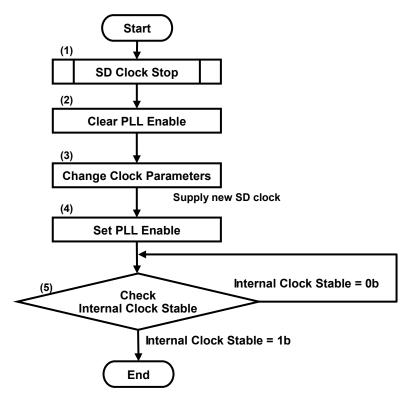

| 3.2.3 SD Clock Supply and Stop Sequence                             |     |

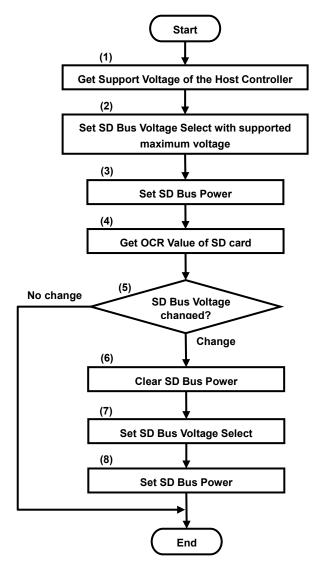

| 3.3 SD Bus Power Control                                            |     |

|                                                                     |     |

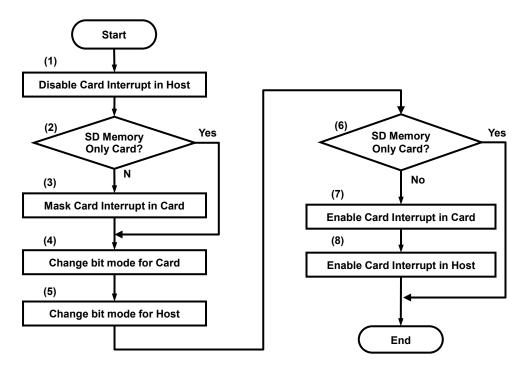

| 3.4 Changing Bus Width                                              |     |

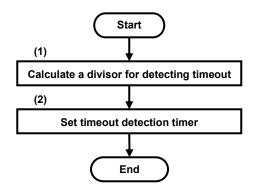

| 3.5 Timeout Setting on DAT Line                                     | 159 |

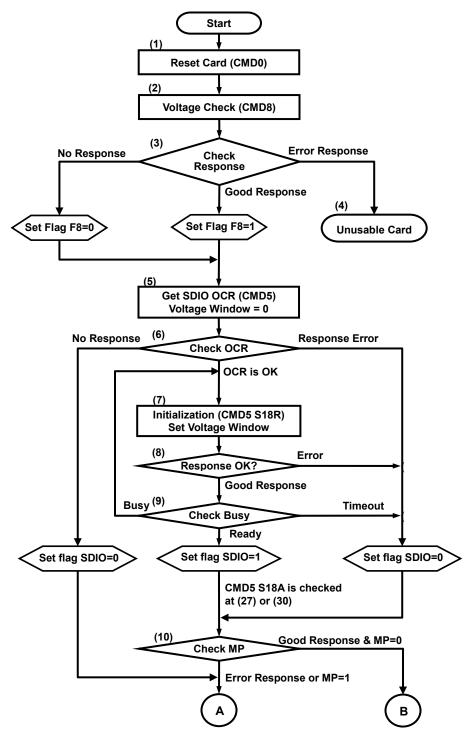

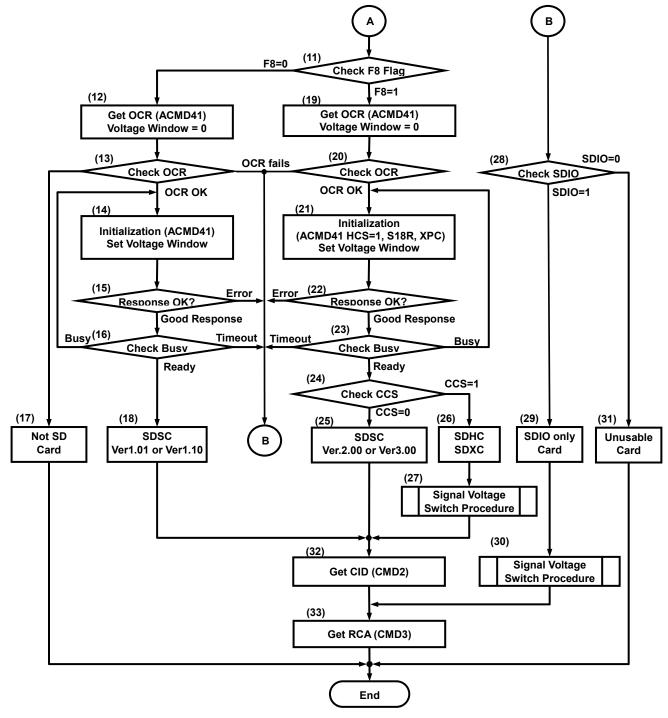

| 3.6 Card Initialization and Identification (for SD I/F)             |     |

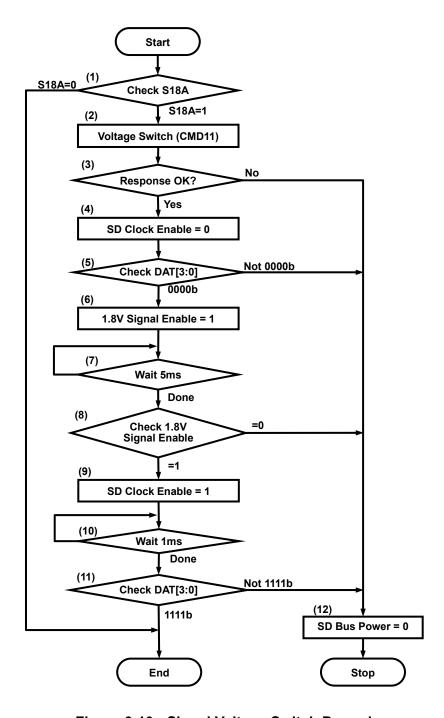

| 3.6.1 Signal Voltage Switch Procedure (for UHS-I)                   | 164 |

| 3.7 SD Transaction Generation                                       | 166 |

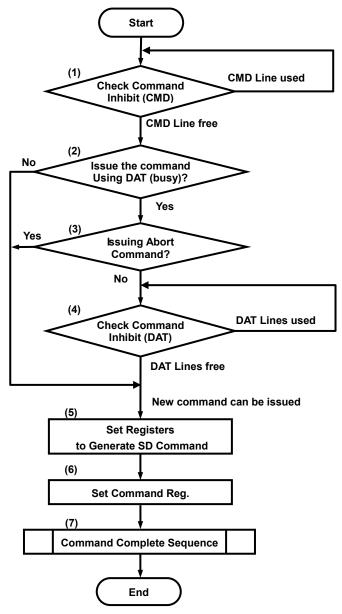

| 3.7.1 Transaction Control without Data Transfer Using DAT Line      | 167 |

| 3.7.1.1 The Sequence to Issue an SD Command                         | 167 |

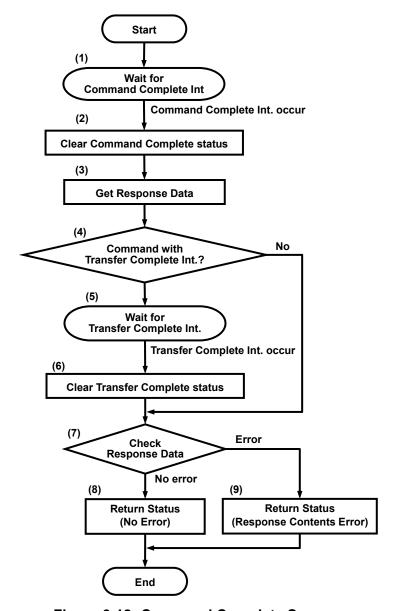

| 3.7.1.2 The Sequence to Finalize a Command                          | 169 |

| 3.7.2 Transaction Control with Data Transfer Using DAT Line         | 170 |

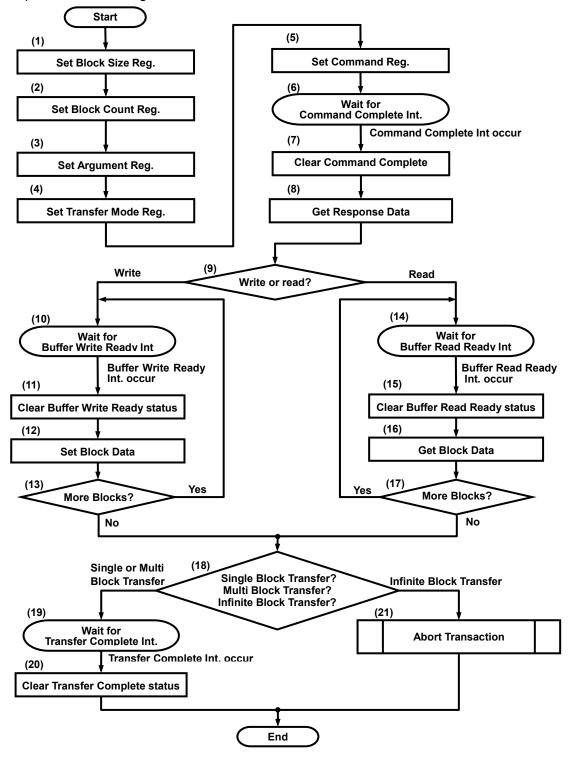

| 3.7.2.1 Not using DMA                                               | 171 |

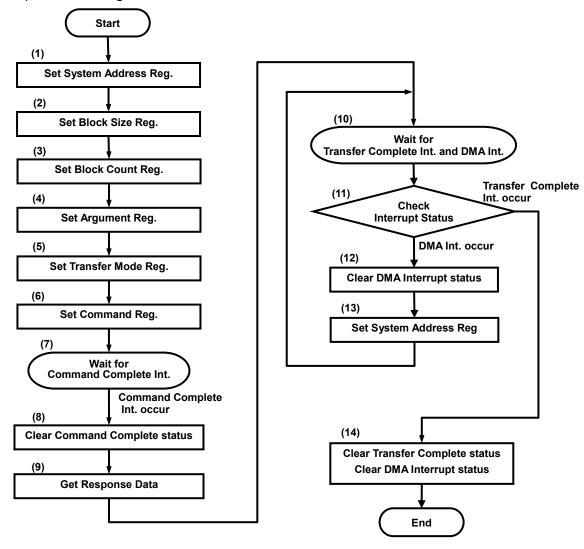

| 3.7.2.2 Using SDMA                                                  |     |

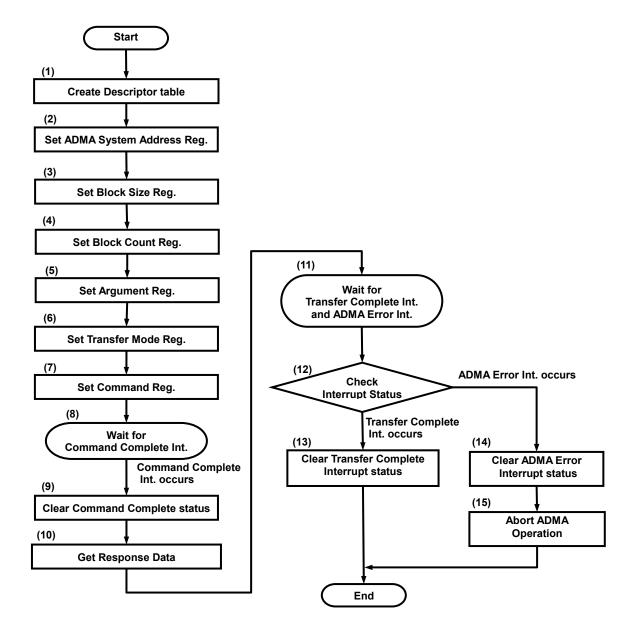

| 3.7.2.3 Using ADMA                                                  | 175 |

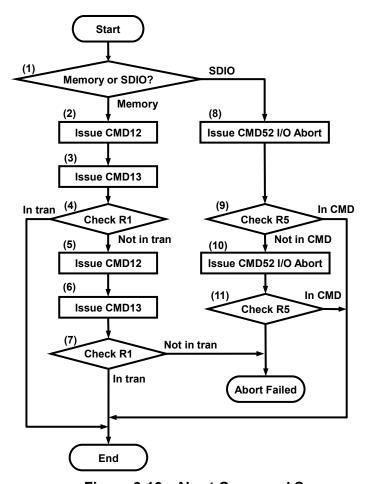

| 3.8 Abort Transaction                                               | 177 |

| 3.8.1 Abort Command Sequence                                        |     |

|                                                                     |     |

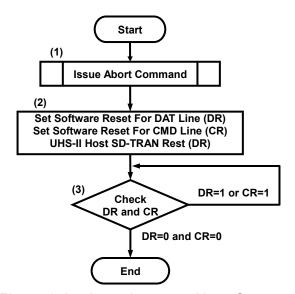

| 3.8.2 Asynchronous Abort                                            | 1/8 |

| 3.8.3 Synchronous Abort                                          |     |

|------------------------------------------------------------------|-----|

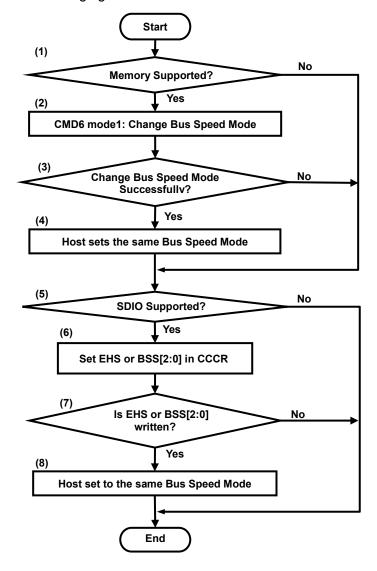

| 3.9 Changing Bus Speed Mode                                      |     |

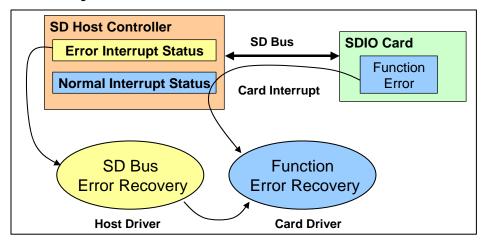

| 3.10 Error Recovery                                              |     |

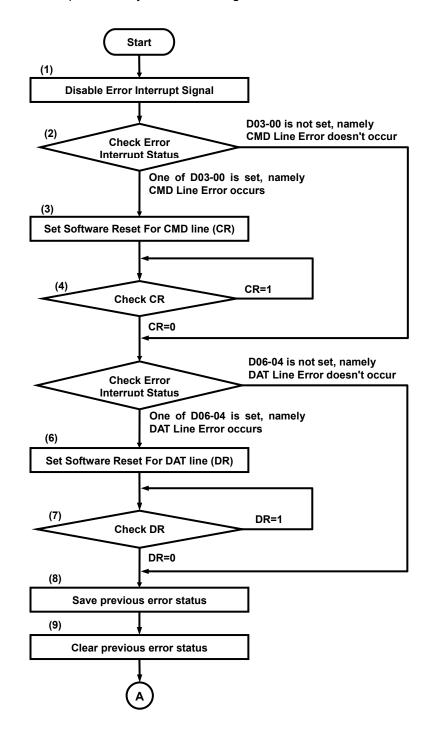

| 3.10.1 Error Interrupt Recovery                                  |     |

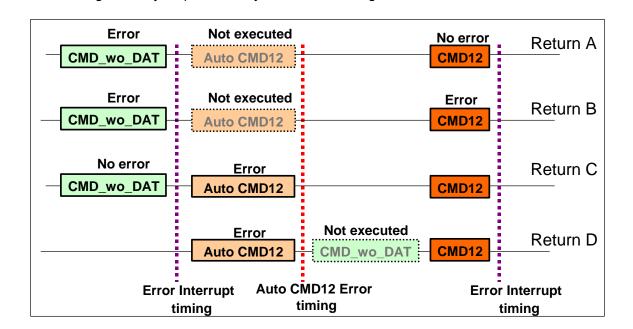

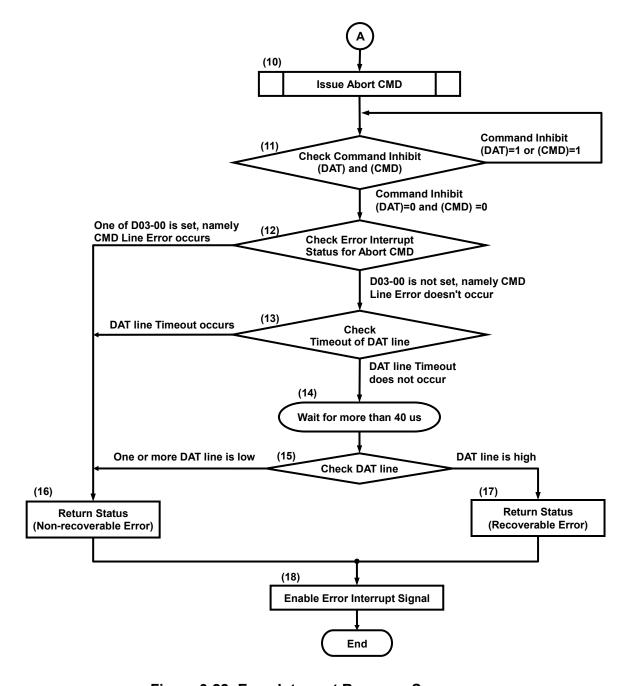

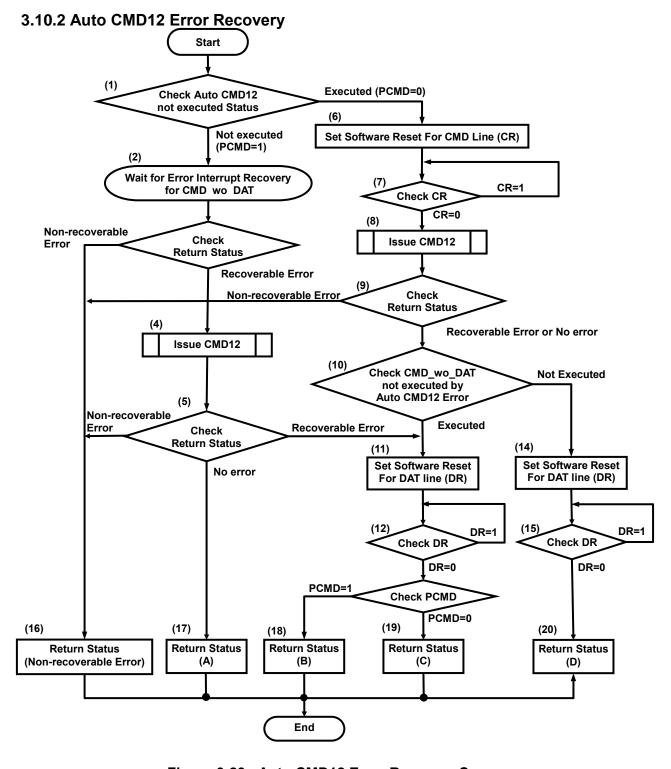

| 3.10.2 Auto CMD12 Error Recovery                                 | 187 |

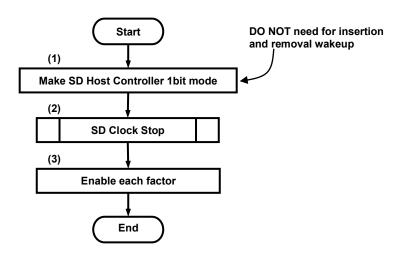

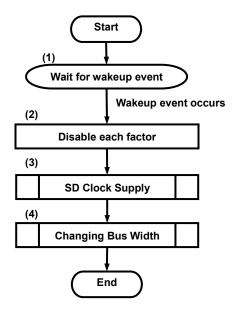

| 3.11 Wakeup Control (Optional)                                   | 189 |

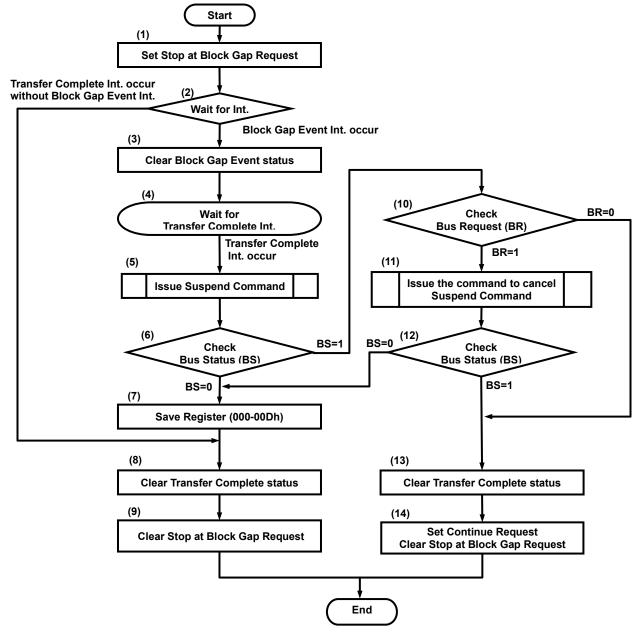

| 3.12 Suspend/Resume (Optional, Not Supported from Version 4.00)  | 191 |

| 3.12.1 Suspend Sequence                                          |     |

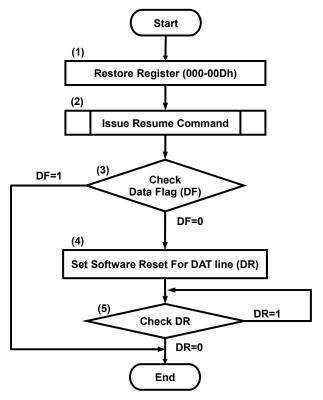

| 3.12.2 Resume Sequence                                           |     |

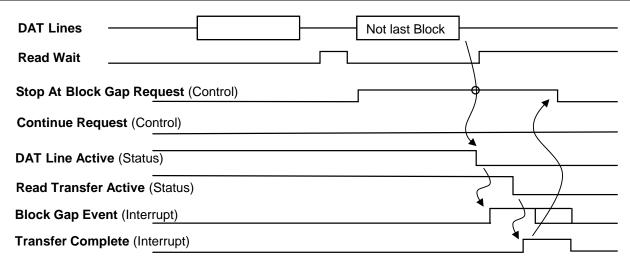

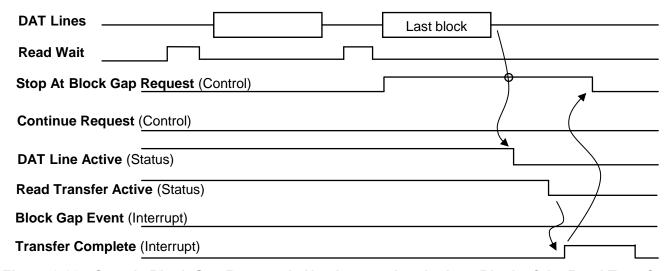

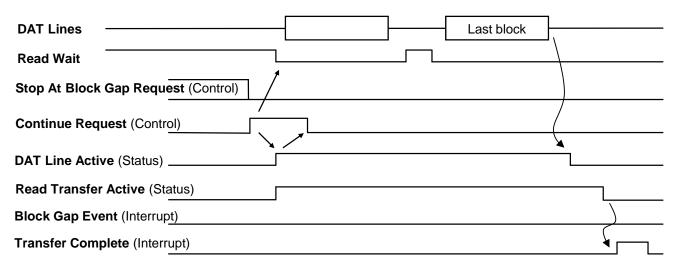

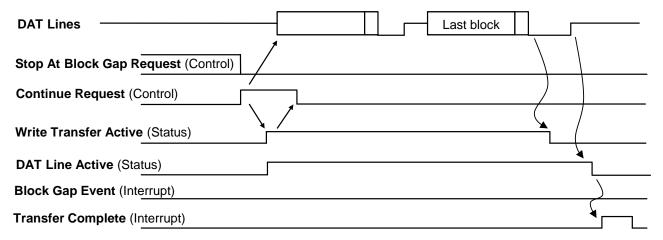

| 3.12.3 Stop At Block Gap / Continue Timing for Read Transaction  | 194 |

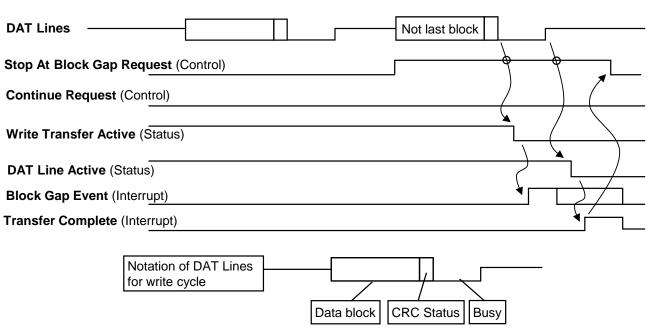

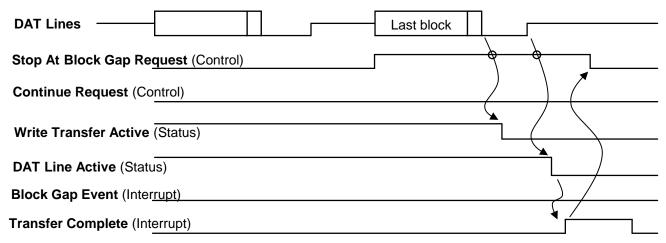

| 3.12.4 Stop At Block Gap / Continue Timing for Write Transaction | 196 |

| 3.13 UHS-II Operation                                            | 198 |

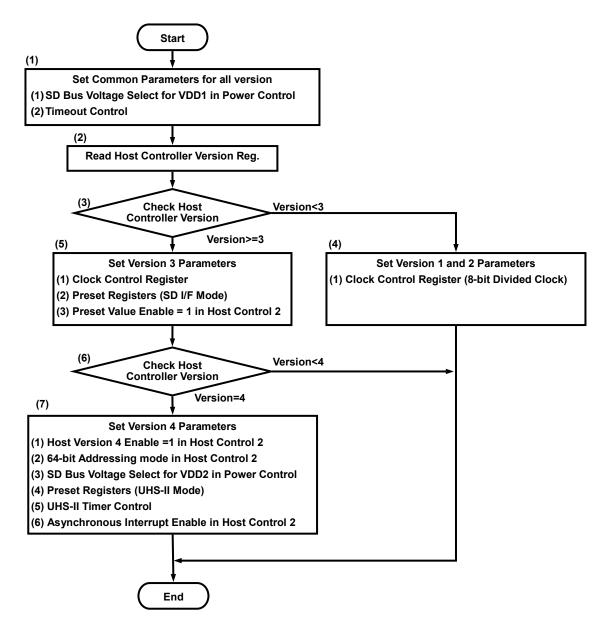

| 3.13.1 Host Controller Setup Sequence                            |     |

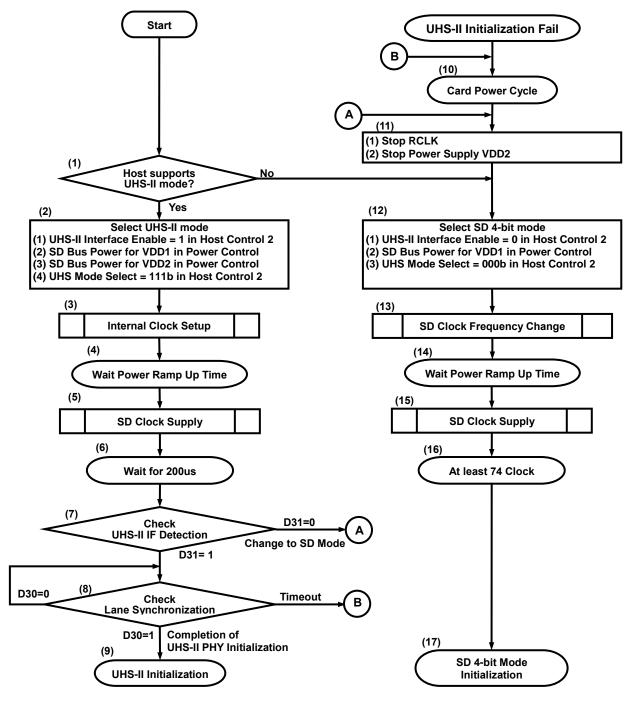

| 3.13.2 Card Interface Detection Sequence                         |     |

| 3.13.3 UHS-II Card Initialization                                | 203 |

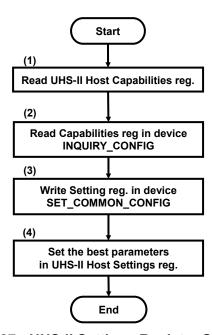

| 3.13.4 UHS-II Settings Register Setup Sequence                   |     |

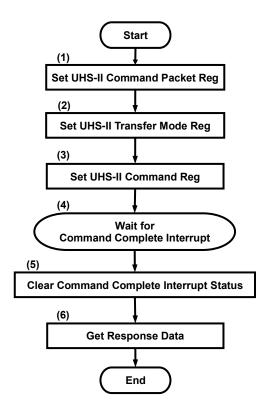

| 3.13.5 UHS-II CCMD Packet Issuing                                |     |

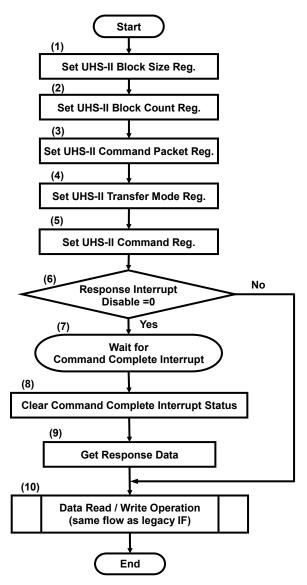

| 3.13.6 UHS-II DCMD Packet Issuing                                |     |

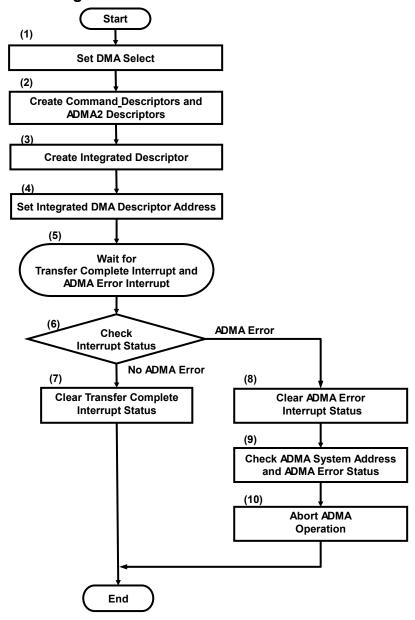

| 3.13.7 Data Transfer Using ADMA3                                 |     |

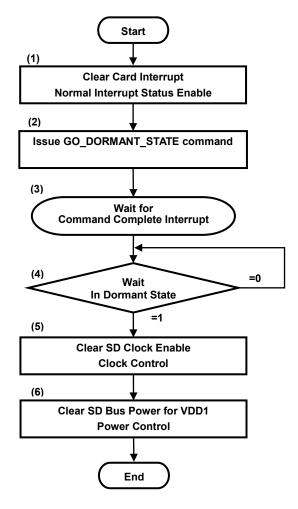

| 3.13.8 Entering Dormant or Hibernate Mode                        |     |

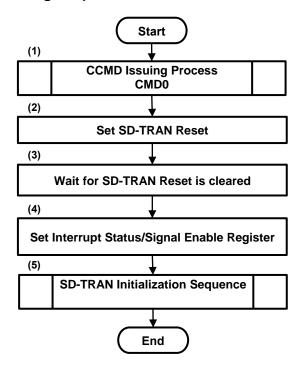

| 3.13.9 SD-TRAN Reset Issuing Sequence                            |     |

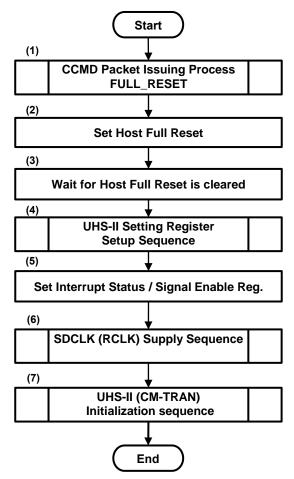

| 3.13.10 Host Full Reset Issuing Sequence                         | 209 |

| A.1 Reference                                                    | 210 |

| B.1 Abbreviations and Terms                                      |     |

| C.1 Register Maps                                                | 212 |

| C.2 SD Controller Configuration Register MAP                     | 213 |

| C.3 PCI Configuration Register                                   | 214 |

| C.3.1 Class Code Register (Offset 09h)                           |     |

| C.3.2 Base Address Register (Offset 10h)                         | 215 |

| C.3.3 Slot Information Register (Offset 40h)                     | 216 |

| C.4 The Relation between Device State. Power and Clock           | 217 |

| C.4.1 Power Management in SD Mode                                | 217 |

| C.4.2 Power Management in UHS-II Mode                            |     |

| C.4.3 Internal Clock Control                                     |     |

| C.5 Generate PME Interrupt by the Wakeup Events                  |     |

| E.1 UHS-II Packet Header Check                                   | 220 |

| E.1.1 An Example of Packet Header Check by Host                  | 220 |

| E.1.2 An Example of Unnecessary Packet Elimination               | 220 |

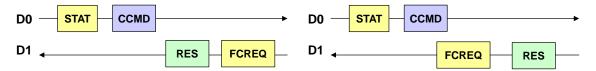

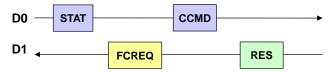

| E.2 CCMD Read Transaction during CTS                             | 221 |

# **Table of Figures**

| Figure 1-1: Host Hardware and Driver Architecture                                         | 1  |

|-------------------------------------------------------------------------------------------|----|

| Figure 1-2: Classification of the Host Controller Register Map                            |    |

| Figure 1-3: Register Map for Multiple Slots Controller                                    | 3  |

| Figure 1-4: Suspend and Resume Mechanism                                                  | 5  |

| Figure 1-5: Buffer Size Relation between Host and Card                                    | 8  |

| Figure 1-6: Logical Relation for Interrupt Registers                                      | 9  |

| Figure 1-7: Block Diagram of Host Controller                                              |    |

| Figure 1-8: Block Diagram of ADMA2                                                        | 15 |

| Figure 1-9: An Example of ADMA2 Data Transfer                                             | 16 |

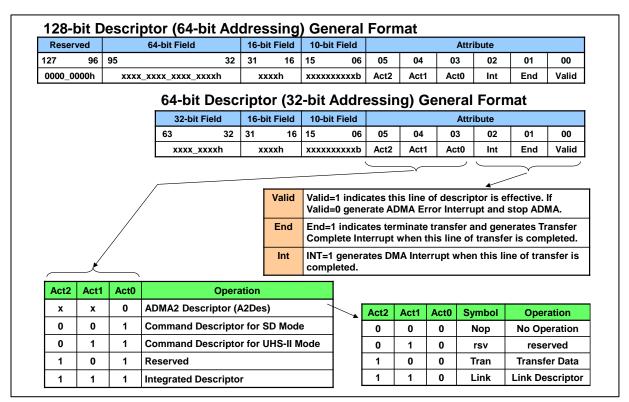

| Figure 1-10 : General Descriptor Table Format                                             | 17 |

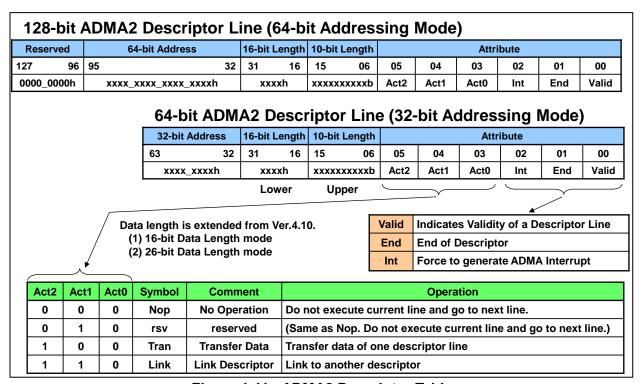

| Figure 1-11 : ADMA2 Descriptor Table                                                      |    |

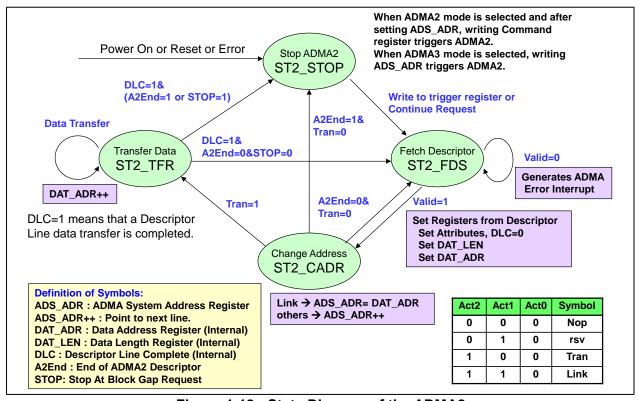

| Figure 1-12: State Diagram of the ADMA2                                                   | 19 |

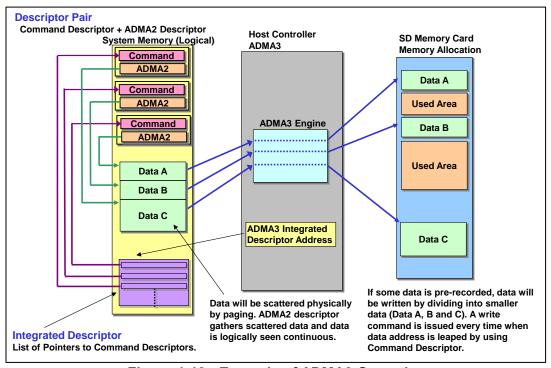

| Figure 1-13 : Example of ADMA3 Operation                                                  | 22 |

| Figure 1-14: State Diagram of the ADMA3                                                   | 23 |

| Figure 1-15 : Command Descriptor Format                                                   |    |

| Figure 1-16 : Integrated Descriptor Format                                                | 25 |

| Figure 1-17 : Concept of How to Retry Command                                             | 29 |

| Figure 2-1: 32-bit Block Count / (SDMA System Address) Register                           | 36 |

| Figure 2-2 : Block Size Register                                                          | 37 |

| Figure 2-3: 16-bit Block Count Register                                                   | 39 |

| Figure 2-4 : Argument Register                                                            | 40 |

| Figure 2-5 : Transfer Mode Register                                                       | 41 |

| Figure 2-6 : Command Register                                                             |    |

| Figure 2-7 : Response Register                                                            | 48 |

| Figure 2-8: Buffer Data Port Register                                                     | 49 |

| Figure 2-9 : Present State Register                                                       | 50 |

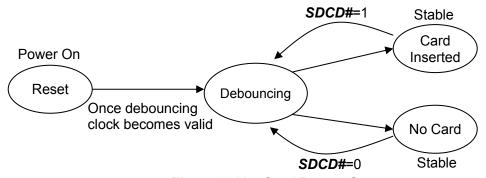

| Figure 2-10 : Card Detect State                                                           | 54 |

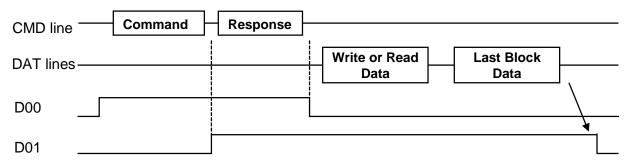

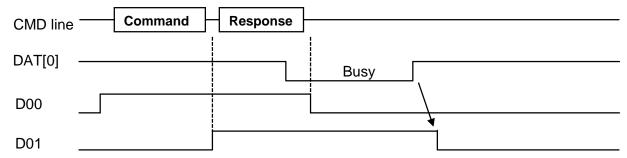

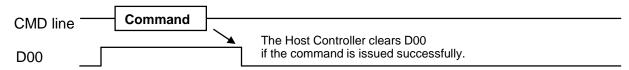

| Figure 2-11: Timing of Command Inhibit (DAT) and Command Inhibit (CMD) with Data Transfer | 59 |

| Figure 2-12: Timing of Command Inhibit (DAT) for the Case of Response with Busy           | 59 |

| Figure 2-13: Timing of Command Inhibit (CMD) for the Case of No Response Command          | 59 |

| Figure 2-14 : Host Control 1 Register                                                     | 60 |

| Figure 2-15 : Power Control Register                                                      | 63 |

| Figure 2-16: Block Gap Control Register                                                   | 65 |

| Figure 2-17: Wakeup Control Register                                                      | 67 |

| Figure 2-18 : Clock Control Register                                                      | 68 |

| Figure 2-19 : Timeout Control Register                                                    | 73 |

| Figure 2-20 : Software Reset Register                                                     | 74 |

| Figure 2-21 : Normal Interrupt Status Register                                            | 76 |

| Figure 2-22 : Error Interrupt Status Register                                             |    |

| Figure 2-23 : Normal Interrupt Status Enable Register                                     | 86 |

| Figure 2-24: Error Interrupt Status Enable Register                                       | 88 |

| Figure 2-25 : Normal Interrupt Signal Enable Register                                     | 90 |

| Figure 2-26 : Error Interrupt Signal Enable Register                                      | 92 |

| Figure 2-27 : Auto CMD Error Status Register                                              | 94 |

| Figure 2-28: Host Control 2 Register                                                      | 96 |

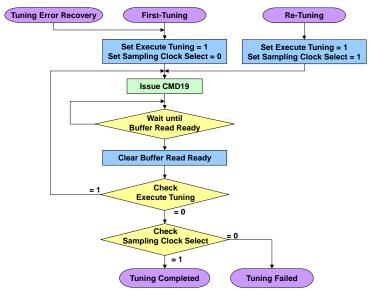

| Figure 2-29 : Sampling Clock Tuning Procedure (UHS-I only)                                |    |

| Figure 2-30 : Capabilities Register                                                       |    |

| Figure 2-31 : Maximum Current Capabilities Register                                       |    |

| Figure 2-32 : Force Event Register for Auto CMD Error Status                              |    |

| Figure 2-33 : Force Event Register for Error Interrupt Status                             |    |

# **SD Host Controller Simplified Specification Version 4.20**

| Figure 2-34 : ADMA Error Status Register                                                    | 115 |

|---------------------------------------------------------------------------------------------|-----|

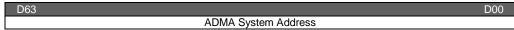

| Figure 2-35 : ADMA System Address Register                                                  | 116 |

| Figure 2-36 : Fields of One Preset Value Register                                           | 117 |

| Figure 2-37 : ADMA3 Integrated Descriptor Address Register                                  | 119 |

| Figure 2-38 : UHS-II Block Size Register                                                    |     |

| Figure 2-39: UHS-II Block Count Register                                                    | 121 |

| Figure 2-40 : UHS-II Transfer Mode Register                                                 | 122 |

| Figure 2-41: UHS-II Command Register                                                        | 125 |

| Figure 2-42: UHS-II MSG Select Register                                                     | 126 |

| Figure 2-43 : UHS-II MSG Register                                                           | 127 |

| Figure 2-44: UHS-II Device Interrupt Status Register                                        |     |

| Figure 2-45 : UHS-II Device Select Register                                                 |     |

| Figure 2-46: UHS-II Device Interrupt Code Register                                          |     |

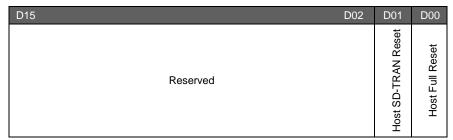

| Figure 2-47: UHS-II Software Reset Register                                                 |     |

| Figure 2-48: UHS-II Timeout Control Register                                                |     |

| Figure 2-49 : UHS-II Error Interrupt Status Register                                        |     |

| Figure 2-50 : UHS-II Error Interrupt Status Enable Register                                 |     |

| Figure 2-51 : UHS-II Error Interrupt Signal Enable Register                                 |     |

| Figure 2-52 : Register format of Pointer Register                                           |     |

| Figure 2-53 : Slot Interrupt Status Register                                                |     |

| Figure 2-54: Host Controller Version Register                                               |     |

| Figure 2-55 : UHS-II General Settings Register                                              |     |

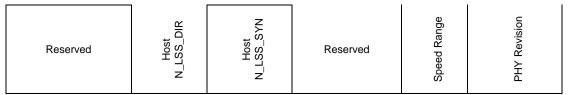

| Figure 2-56: UHS-II PHY Settings Register                                                   |     |

| Figure 2-57: UHS-II LINK/TRAN Settings Register                                             |     |

| Figure 2-58 : UHS-II General Capabilities Register                                          |     |

| Figure 2-59: UHS-II PHY Capabilities Register                                               |     |

| Figure 2-60 : UHS-II LINK/TRAN Capabilities Register                                        |     |

| Figure 2-61 : Force Event for UHS-II Error Interrupt Status Register                        |     |

| Figure 2-62 : Embedded Control Register                                                     |     |

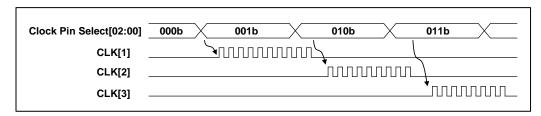

| Figure 2-63 : An Example Timing of Selecting Clock Pin                                      |     |

| Figure 3-1 : Double Box Notation                                                            |     |

| Figure 3-2: SD Card Detect Sequence                                                         |     |

| Figure 3-3: Internal Clock Setup Sequence                                                   |     |

| Figure 3-4: SD Clock Supply and Stop Sequence                                               |     |

| Figure 3-5: SD Clock Change Sequence                                                        |     |

| Figure 3-6: SD Bus Power Control Sequence                                                   |     |

| Figure 3-7: Change Bus Width Sequence                                                       |     |

| Figure 3-8: Timeout Setting Sequence                                                        |     |

| Figure 3-9 : Card Initialization and Identification                                         |     |

| Figure 3-10 : Signal Voltage Switch Procedure                                               |     |

| Figure 3-11: SD Command Issue Sequence                                                      |     |

| Figure 3-12: Command Complete Sequence                                                      |     |

| Figure 3-13: Transaction Control with Data Transfer Using DAT Line Sequence (Not using DMA) |     |

| Figure 3-14: Transaction Control with Data Transfer Using DAT Line Sequence (Using SDMA)    |     |

| Figure 3-15: Transaction Control with Data Transfer Using DAT Line Sequence (Using ADMA)    |     |

| Figure 3-16 : Abort Command Sequence                                                        |     |

| Figure 3-17: Asynchronous Abort Sequence                                                    |     |

| Figure 3-18: Synchronous Abort Sequence                                                     |     |

| Figure 3-19: Bus Speed Mode Setting for Combo Card                                          | 180 |

| Figure 3-20 : Error Report and Recovery                                                     |     |

| Figure 3-21: Return Status of Auto CMD12 Error Recovery                                     |     |

| Figure 3-22: Error Interrupt Recovery Sequence                                              |     |

| Figure 3-23 : Auto CMD12 Error Recovery Sequence                                            |     |

|                                                                                             |     |

# SD Host Controller Simplified Specification Version 4.20

| Figure 3-24: Wakeup Control before Standby Mode                                                | 189 |

|------------------------------------------------------------------------------------------------|-----|

| Figure 3-25: Wakeup from Standby                                                               |     |

| Figure 3-26 : The Sequence for Suspend                                                         |     |

| Figure 3-27: The Sequence for Resume                                                           |     |

| Figure 3-28: Wait Read Transfer by Stop At Block Gap Request                                   |     |

| Figure 3-29: Stop At Block Gap Request is Not Accepted at the Last Block of the Read Transfer  |     |

| Figure 3-30 : Continue Read Transfer by Continue Request                                       |     |

| Figure 3-31: Wait Write Transfer by Stop At Block Gap Request                                  | 196 |

| Figure 3-32: Stop At Block Gap Request is Not Accepted at the Last Block of the Write Transfer | 197 |

| Figure 3-33 : Continue Write Transfer by Continue Request                                      |     |

| Figure 3-34: Host Controller Setup Sequence                                                    | 198 |

| Figure 3-35 : Card Interface Detection Sequence                                                | 200 |

| Figure 3-36: Latency Compensation for Reading UHS-II IF Detection                              | 202 |

| Figure 3-37: UHS-II Settings Register Setup Sequence                                           |     |

| Figure 3-38: UHS-II CCMD Packet Issuing                                                        |     |

| Figure 3-39: UHS-II DCMD Packet Issuing                                                        | 205 |

| Figure 3-40 : Data Transfer Using ADMA3                                                        |     |

| Figure 3-41 : Entering Dormant or Hibernate Mode                                               |     |

| Figure 3-42 : SD-TRAN Reset Issuing Sequence                                                   |     |

| Figure 3-43 : Host Full Reset Issuing Sequence                                                 |     |

| Figure C- 1 : Register Set for PCI Device (Example for 2 slots)                                | 212 |

| Figure C- 2: Vendor Specific Register Area Extension                                           |     |

| Figure C- 3 : PCI Config. Class Code Register                                                  |     |

| Figure C- 4: PCI Config. Base Address Register for 256Byte Register Map                        |     |

| Figure C- 5 : PCI Config. Base Address Register for 512Byte Register Map                       |     |

| Figure C- 6: PCI Config. Slot Information Register                                             |     |

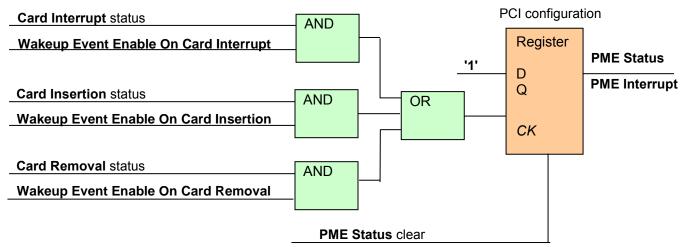

| Figure C- 7 : Condition to Generate PME Interrupt                                              | 218 |

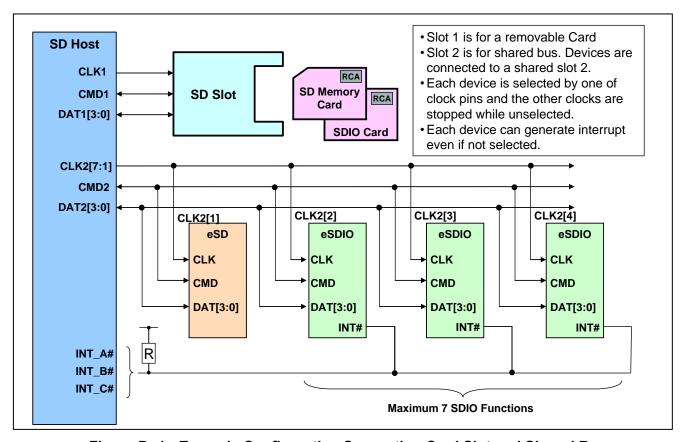

| Figure D- 1 : Example Configuration Supporting Card Slot and Shared Bus                        | 219 |

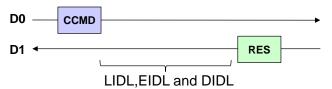

| Figure E - 1 : CCMD Read Transaction during CTS                                                | 221 |

# **Table of Tables**

| Table 1-1 : Supported Registers                                              | 2  |

|------------------------------------------------------------------------------|----|

| Table 1-2 : Registers to Generate SD Command                                 | 4  |

| Table 1-3: Relations between Address and Byte Enable                         |    |

| Table 1-4 : Available Byte Enable Pattern for Buffer Data Port Register      |    |

| Table 1-5 : Interrupt Signal Table                                           |    |

| Table 1-6: Wakeup Signal Table                                               |    |

| Table 1-7: Summary of Register Status for Data Transfer                      |    |

| Table 1-8 : Power State Definition                                           | 12 |

| Table 1-9: Relation between Auto CMD12 and CMD_wo_DAT                        | 13 |

| Table 1-10: Controlling SDCLK by the SD Bus Power and SD Clock Enable        | 14 |

| Table 1-11 : 64-bit Address Descriptor Table                                 |    |

| Table 1-12 : ADMA2 16-bit Length Mode                                        |    |

| Table 1-13 : ADMA2 26-bit Length Mode                                        |    |

| Table 1-14 : ADMA2 States                                                    |    |

| Table 1-15 : ADMA3 States                                                    |    |

| Table 1-16: Host Controller Data Transfer Length                             |    |

| Table 1-17: Summary of Command Issuing During Data Transfer                  |    |

| Table 2-1 : SD Host Controller Register Map (0FFh – 000h)                    |    |

| Table 2-2 : SD Host Controller Register Map (1FFh – 100h)                    |    |

| Table 2-3: Register (and Register Bit-Field) Types                           |    |

| Table 2-4: SDMA System Address / Argument 2 Register                         |    |

| Table 2-5 : Block Size Register                                              |    |

| Table 2-6: 16-bit Block Count Register                                       | 39 |

| Table 2-7 : Argument Register                                                |    |

| Table 2-8 : Transfer Mode Register                                           |    |

| Table 2-9 : Determination of Transfer Type                                   |    |

| Table 2-10 : Command Register                                                |    |

| Table 2-11: Relation between Parameters and the Name of Response Type        |    |

| Table 2-12 : Response Register                                               |    |

| Table 2-13 : Response Bit Definition for Each Response Type                  | 48 |

| Table 2-14: Buffer Data Port Register                                        |    |

| Table 2-15 : Present State Register (Part 1)                                 | 54 |

| Table 2-16: Present State Register (Part 2)                                  |    |

| Table 2-17: Host Control 1 Register                                          | 62 |

| Table 2-18 : Power Control Register                                          |    |

| Table 2-19 : Block Gap Control Register                                      |    |

| Table 2-20 : Wakeup Control Register                                         |    |

| Table 2-21 : Clock Control Register                                          | 72 |

| Table 2-22 : Timeout Control Register                                        | 73 |

| Table 2-23 : Software Reset Register                                         | 75 |

| Table 2-24: Normal Interrupt Status Register                                 | 81 |

| Table 2-25 : Error Interrupt Status Register                                 |    |

| Table 2-26: The Relation between Command CRC Error and Command Timeout Error | 85 |

| Table 2-27: Normal Interrupt Status Enable Register                          | 87 |

| Table 2-28 : Error Interrupt Status Enable Register                          |    |

| Table 2-29 : Normal Interrupt Signal Enable Register                         |    |

| Table 2-30 : Error Interrupt Signal Enable Register                          | 93 |

| Table 2-31 : Auto CMD Error Status Register                                  | 95 |

| Table 2-32: The Relation between CRC Error and Timeout Error for Auto CMD    |    |

| Table 2-33 : Host Control 2 Register                                         |    |

# **SD Host Controller Simplified Specification Version 4.20**

| Table 2-34 : Capabilities Register (Part 1)                             | .107  |

|-------------------------------------------------------------------------|-------|

| Table 2-35: 64-bit System Address Support depends on Versions           | .108  |

| Table 2-36 : Capabilities Register (Part 2)                             |       |

| Table 2-37 : Maximum Current Capabilities Register                      |       |

| Table 2-38 : Maximum Current Value Definition                           |       |

| Table 2-39 : Force Event Register for Auto CMD Error Status             | 112   |

| Table 2-40 : Force Event for Error Interrupt Status Register            |       |

| Table 2-41 : ADMA Error Status Register                                 |       |

| Table 2-42 : ADMA System Address Register                               |       |

| Table 2-43 : Preset Value Registers                                     |       |

| Table 2-44 : Preset Value Register Select Condition                     |       |

| Table 2-45 : Fields of One Preset Value Register                        |       |

| Table 2-46 : Integrated DMA Descriptor Address Register                 |       |

| Table 2-47 : UHS-II Block Size Register                                 |       |

| Table 2-48 : Block Count Register                                       |       |

| Table 2-49 : UHS-II Command Packet Register                             |       |

| Table 2-50 : UHS-II Transfer Mode Register                              |       |

|                                                                         |       |

| Table 2-51 : UHS-II Command Register                                    |       |

| Table 2-52 : UHS-II Response Register                                   |       |

| Table 2-53: UHS-II MSG Select Register                                  |       |

| Table 2-54: UHS-II Device Interrupt Status Register                     |       |

| Table 2-55: UHS-II Device Select Register                               |       |

| Table 2-56: UHS-II Software Reset Register                              |       |

| Table 2-57: UHS-II Timeout Control Register                             |       |

| Table 2-58 : UHS-II Error Interrupt Status Register                     |       |

| Table 2-59: UHS-II Error Interrupt Status Enable Register               |       |

| Table 2-60 : UHS-II Error Interrupt Signal Enable Register              |       |

| Table 2-61: Pointer Registers for mFF-100h Area                         |       |

| Table 2-62 : Slot Interrupt Status Register                             |       |

| Table 2-63 : Host Controller Version                                    |       |

| Table 2-64: UHS-II Settings Registers                                   |       |

| Table 2-65 : UHS-II General Settings Register                           |       |

| Table 2-66: UHS-II PHY Settings Register                                |       |

| Table 2-67: UHS-II LINK/TRAN Settings Register                          |       |

| Table 2-68: UHS-II Host Capabilities Registers                          |       |

| Table 2-69: UHS-II General Capabilities Register                        |       |

| Table 2-70: UHS-II PHY Capabilities Register                            |       |

| Table 2-71: UHS-II LINK/TRAN Capabilities Register                      | 146   |

| Table 2-72 : Force Event for UHS-II Error Interrupt Status Register     | . 147 |

| Table 2-73 : Embedded Control Register                                  | 150   |

| Table 3-1 Suspend/Resume Condition                                      | .192  |

|                                                                         |       |

| Table C- 1: PCI Configuration Register for Standard SD Host Controller  | 213   |

| Table C- 2 : PCI Config. Class Code Register                            | .214  |

| Table C- 3: PCI Config. Base Address Register for 256Byte Register Map  | 215   |

| Table C- 4 : PCI Config. Base Address Register for 512Byte Register Map |       |

| Table C- 5 : PCI Config. Slot Information Register                      |       |

| Table C- 6 : The Relation between Device State, Power and Clock         | 217   |

| Table C- 7 : The Relation between Device State, Power and Clock         |       |

|                                                                         |       |

| Table E - 1 : An Example of Packet Header Check by Host                 | 220   |

# 1. Overview of the SD Standard Host

The Secure Digital (SD) Host Standard Specification is the SD Association's (SDA) guideline for designing SD Host Controllers and related vendor products. Within the scope of the SD Associations adherence to this specification is not mandatory. It is the Host Controller vendor's responsibility to design products that comply with the SD Specification and where possible to use standard Host Drivers. OS vendor, IHVs and OEMs may require compliance according to their own policies so adherence is recommended.

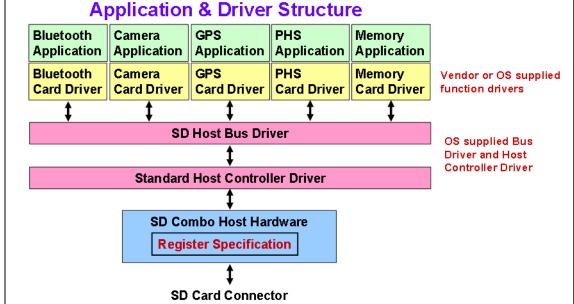

#### 1.1 Scope of the Standard SD Host Bluetooth Camera GPS

Figure 1-1: Host Hardware and Driver Architecture

Defining a standard SD Host Controller is intended to promote increase of SD host products that can use SD memory cards and SDIO cards. Host Controller standardization enables Operating System (OS) Vendors to develop Host Driver (SD Host Bus Driver and Standard Host Controller Driver) that works with Host Controllers from any vendor.

Applications may in addition require the Card Drivers that supplied by card vendors or OS vendor. The Card Drivers communicate with the SD Host Bus Driver using a driver interface specified by the OS.

#### Implementation Note:

This specification can be applied to any system bus interface. The interface between the Host Driver and its parent system driver (if any) is not defined by this specification.

# 1.2 Register Map

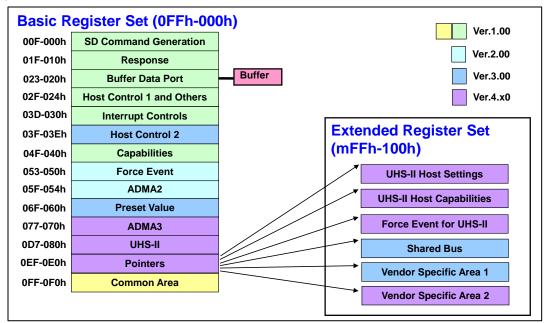

Figure 1-2: Classification of the Host Controller Register Map

The standard register map is classified in 18 parts listed below. The Host Controller shall support byte, word and double word accesses to these registers. Reserved bits in all registers shall be fixed to zero. The Host Controller shall ignore writes to reserved bits; however, the Host Driver should write them as zero to ensure compatibility with possible future revisions to this Specification.

| No | Register Name             | Version |      |      | Comment |      |                                         |

|----|---------------------------|---------|------|------|---------|------|-----------------------------------------|

|    |                           | 1.00    | 2.00 | 3.00 | 4.00    | 4.10 |                                         |

| 1  | SD command generation     | М       | М    | М    | М       | М    | 32-bit Block Count from Ver.4.10        |

| 2  | Response                  | M       | М    | М    | М       | М    |                                         |

| 3  | Buffer Data port          | М       | М    | М    | М       | М    |                                         |

| 4  | Host control 1 and Others | М       | М    | М    | М       | М    |                                         |

| 5  | Interrupt controls        | М       | М    | М    | М       | М    | Some fields will be added in later ver. |

| 6  | Capabilities              | М       | M    | М    | М       | М    | Some fields will be added in later ver. |

| 7  | Host Control 2            | N/A     | N/A  | М    | М       | М    | For UHS-I Support                       |

| 8  | Force Event               | N/A     | М    | М    | М       | М    | For test                                |

| 9  | ADMA2                     | N/A     | 0    | М    | М       | М    |                                         |

| 10 | Preset Value              | N/A     | N/A  | M    | М       | М    |                                         |

| 11 | ADMA3                     | N/A     | N/A  | N/A  | N/A     | 0    | ADMA3 from Ver.4.10                     |

| 12 | UHS-II                    | N/A     | N/A  | N/A  | 0       | 0    |                                         |

| 13 | Pointers                  | N/A     | N/A  | N/A  | М       | M    | Mandatory if mFFh-100h is used          |

| 14 | Common Area               | M       | M    | M    | М       | M    |                                         |

| 15 | UHS-II Settings           | N/A     | N/A  | N/A  | 0       | 0    | Mandatory if UHS-II is supported        |

| 16 | UHS-II Host Capabilities  | N/A     | N/A  | N/A  | 0       | 0    | Mandatory if UHS-II is supported        |

| 17 | UHS-II Force Event        | N/A     | N/A  | N/A  | 0       | 0    | Mandatory if UHS-II is supported        |

| 18 | Embedded Control          | N/A     | N/A  | 0    | 0       | 0    | Moved to 1FFh-100h                      |

M: Mandatory, O: Optional, N/A: Not Available

**Table 1-1: Supported Registers**

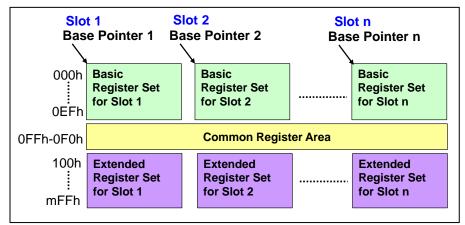

## 1.3 Multiple Slot Support

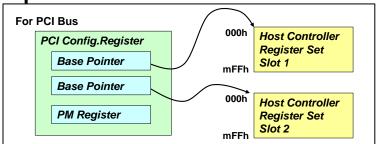

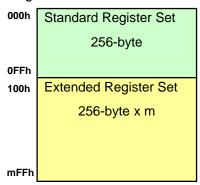

One Standard Register Set is defined for each slot. If the Host Controller has two slots, two register sets is required. Each slot is controlled independently. This enables support for combinations of bus interface voltage, bus timing and SD Clock frequencies.

Figure 1-3: Register Map for Multiple Slots Controller

Figure 1-3 shows the register map for a multiple slot Host Controller. The Host Driver shall determine the number of slots and base pointers to each slot's Basic Register Set using PCI Configuration register or vendor specific methods. Offsets from 0F0h to 0FFh are reserved for the Common register area that defines information for slot control and common status. The common register area is accessible from any slot's register set. This allows software to control each slot independently, since it has access to the *Slot Interrupt Status* register and the *Host Controller Version* register from each register set. From 100h to mFFh, Extended Register Set can be assigned. A parameter "m" denotes integer to determine size of the Extended Register Set.

# 1.4 Supporting DMA

The Host Controller provides a "programmed I/O" method for the Host Driver to transfer data using the *Buffer Data Port* register. Optionally, Host Controller implementers may support data transfer using DMA. The DMA algorithm defined in the SD Host Controller Standard Specification Version 1.00 is called SDMA (Single Operation DMA). Only one SD command transaction can be executed per an SDMA operation. Support of SDMA can be checked by the **SDMA Support** in the *Capabilities* register.

This specification defines a DMA transfer algorithm called ADMA (Advanced DMA). ADMA provides data transfer between system memory and SD card without interruption of CPU execution. Support of ADMA can be checked by the *Capabilities* register. Refer to Section 1.13 for more details about ADMA. When the term "DMA" is used in this document, it applies to both SDMA and ADMA.

Prior to using DMA, the Host Driver shall confirm that both the Host Controller and the system bus support it (PCI bus can support DMA). DMA shall support both single block and multiple-block transfers. Host Controller registers shall remain accessible for issuing non-DAT line commands during a DMA transfer execution (Not applicable to UHS-II mode). The result of a DMA transfer shall be the same regardless of the system bus data transfer method.

The Host Driver can stop and restart a DMA operation by the control bits in the *Block Gap Control* register. By setting **Stop At Block Gap Request**, a DMA operation can be stopped at block gap. By setting **Continue Request**, DMA operation can be restarted. Refer to the *Block Gap Control* register for more details. If an error occurs, DMA operation shall be stopped. Synchronous abort described in Section 3.8.3 should be used to abort DMA transfer instead of asynchronous abort to ensure

cancellation of DMA does not affect system bus operation. Stop operating DMA by using **Stop At Block Gap Request** and then issue abort command to stop card data transfer. After that, Host Driver resets the Host Controller by using the **Software Reset For DAT Line** in the *Software Reset* register (SD mode) or the **Host SD-TRAN Reset** in the *UHS-II Software Reset* register (UHS-II mode).

#### 1.5 SD Command Generation

#### 1.5.1 SD Mode Command Generation

|                                            | SDMA<br>Command | ADMA<br>Command           | CPU data<br>Transfer | Non-DAT<br>Transfer |

|--------------------------------------------|-----------------|---------------------------|----------------------|---------------------|

| 32-bit Block Count / (SDMA System Address) | Note 1          | Note 1,2,3                | Note 1,2,3           | No (Protected)      |

| Block Size                                 | Yes             | Yes                       | Yes                  | No (Protected)      |

| 16-bit Block Count                         | Note 3          | Note 3<br>Refer to 1.15.3 | Note 3               | No (Protected)      |

| Argument                                   | Yes             | Yes                       | Yes                  | Yes                 |

| Transfer Mode                              | Yes             | Yes                       | Yes                  | Note 4              |

| Command                                    | Yes             | Yes                       | Yes                  | Yes                 |

- Note 1: If **Host Version 4 Enable** is set to 1 in the *Host Control 2* register, this register is used for *32-bit Block Count* instead of *SDMA System Address*. SDMA start address is moved to *ADMA System Address* register.

- Note 2: Auto CMD23 is supported from Version 3.00 and setting of this register is set to the argument of CMD23 when Auto CMD23 is executed. If **Host Version 4 Enable** =0, Auto CMD23 cannot be used with SDMA. Host Controller Version 4.10 re-defines this register as 32-bit Block Count so that all data transfer modes may use 32-bit Block Count when **Host Version 4 Enable** =1.

- Note 3: Version 2.00 or later uses 16-bit Block Count register or ADMA2 total length to determine transfer length. Additionally, Version 4.10 may use 32-bit Block Count register, which is selected when **Host Version 4**Enable is set to 1 and 16-bit Block Count is set to 0000h.

- Note 4: If Host Version 4 Enable = 0, "No (Protected)". If Host Version 4 Enable = 1, "Yes".

Table 1-2: Registers to Generate SD Command

Table 1-2 shows register settings (at offsets from 000h to 00Fh in the register set) necessary for three types of transactions: SDMA generated transfers, ADMA generated transfers, CPU data transfers (using "programmed I/O") and non-DAT transfers. When initiating a transaction, the Host Driver should program these registers sequentially from 000h to 00Fh. The beginning register offset may be calculated based on the type of transaction. The last written offset shall be always 00Fh because writing to the upper byte of the *Command* register shall trigger issuance of an SD command.

The Host Driver should not read the *SDMA System Address*, *Block Size* and *Block Count* registers during a data transaction unless the transfer is stopped because the value is changing and not stable. To prevent destruction of registers using data transfer when issuing command, the *32-bit Block Count*, *Block Size*, *16-bit Block Count* and *Transfer Mode* registers shall be write protected by the Host Controller while **Command Inhibit (DAT)** is set to 1 in the *Present State* register. (When Host Version 4 Enable =0, the *SDMA System Address* is not protected by this signal.) The Host Driver shall not write the *Argument* and *Command* registers while **Command Inhibit (CMD)** is set to 1.

#### 1.5.2 UHS-II Mode Command Generation

UHS-II Command Packet is generated by setting following registers.

- (1) UHS-II Block Size Register for DCMD(2) UHS-II Block Count Register for DCMD

- (3) UHS-II Command Packet Register for CCMD and DCMD (4) UHS-II Transfer Mode Register for CCMD and DCMD (5) UHS-II Command Register for CCMD and DCMD

Theses registers are correspondent to that of SD Mode registers. UHS-II command packet image is set to *UHS-II Command Packet* register. Host Controller does not analyze this register to issue a command packet. On writing to *UHS-II Command* register, Host Controller issues a command packet.

#### 1.5.2.1 Command Issuing during CTS

When CCMD is issued at CTS of DCMD execution, the RES packet of CCMD is set to the *UHS-II Response* register. If CCMD is other than reset or abort command, DCMD execution continues. For example, this feature may be used for issuing CMD52 during CMD53 execution in case of SDIO. Refer to Section 1.17 for more details about response error check.

#### 1.5.2.2 Support of TID Check

Host Controller Version 4.10 supports TID. Host Controller compares TID of command with TID of all received packets of the same transaction. If TID is not matched, TID Error is set to 1 in the *UHS-II Error Interrupt Status* register and the transaction shall be stopped.

In case of command issuing during CTS, it works if TID in DCMD and TID in CCMD during CTS are set to 0. It also works if different values other than 0 are set to them.

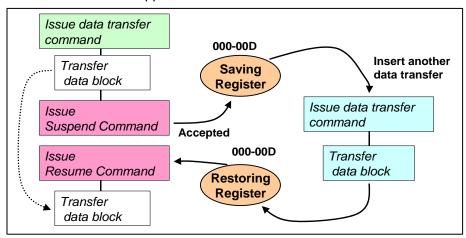

#### 1.6 Suspend and Resume Mechanism (Version 3.00 or less)

Suspend/Resume function is not supported from Version 4.00.

Figure 1-4: Suspend and Resume Mechanism

Support for Suspend/Resume can be determined by checking **Suspend/Resume Support** in the *Capabilities* register. When the SD card accepts a suspend request, the Host Driver saves information in the first 14 bytes registers (that is, offsets 000h-00Dh) before issuing other SD commands. On resuming, the Host Driver restores these registers and then issues the Resume command to continue suspended operation.

The SDIO card sets the **DF** (Resume Data Flag) in the response to the Resume command. (Since the Suspend and Resume commands are CMD52 operations, the response data is actually the Function Select Register in the CCCR.) If **DF** is set to 0, it means the SDIO card cannot continue data transfer while suspended. This bit can be used to control data transfers and interrupt cycles. If the Resume Data Flag is set to 0, no more data is transferred and an interrupt cycle is started if the transaction being resumed is in 4-bit mode. If **DF** is set to 1, data transfers continue. The Suspend/Resume protocol is described in the SDIO Specification (SD Specifications Part E1).

Note: To use Suspend/Resume function, it is necessary that SDIO Card supports the Suspend and Resume commands and Read Wait control.

#### 1.7 Buffer Control

The Host Controller has a data buffer for data transfer. The Host Driver accesses internal buffer through the 32-bit *Buffer Data Port* register. DMA also uses internal buffer to control data transfer between system memory and SD Card.

Buffer Size is determined by setting of block size. Data Transfer Size is determined by setting of block size and block count.

In SD mode, block size is set by *Block Size* register (Offset 004h) and block count is set by 16-bit *Block Count* register (Offset 006h). 16-bit block count limits the maximum data transfer length. The buffer size is determined by setting of the *Block Size* register.

In UHS-II mode, block size is set by *UHS-II Block Size* register (Offset 080h) and block count is set by 32-bit *UHS-II Block Count* register (Offset 084h). There is no limit of data transfer length by 32-bit block count. The buffer size is determined by setting of the Block Size register and **N\_FCU** in the *UHS-II Settings* register as follows:

Buffer Size in UHS-II mode = **UHS-II Block Size** \* **N\_FCU** (Settings)

Followings Sections show some rules to access the buffer.

#### 1.7.1 Control of Buffer Pointer (Non DMA)

Internally, the Host Controller maintains a pointer to control the data buffer. The pointer is not directly accessible by the Host Driver. Every time the *Buffer Data Port* register is accessed, the pointer is incremented depending on amount of data written to the buffer. In order to accommodate a variety of system busses, this pointer shall be implemented regardless of system bus width (8-bit, 16-bit, 32-bit or 64-bit system bus width can be supported). To specify control of the pointer, the Host Controller data buffer interface shall have the following characteristics:

# (6) System Bus Width and Byte Enable Address

8-bit, 16-bit, 32-bit or 64-bit system bus is supported. To specify byte position for *Buffer Data Port* register (4 bytes), Byte Enable (*BE*[]) or Lower Address (*A*[]) is used. Table 1-3 shows the relation between lower address and byte enable depending on system bus width. The *Buffer Data Port* register can be accessed by *BE*[3:0] for 64-bit system bus, which has *BE*[7:0].

| System Bus | A[02] | A[01] | A[00] | BE[3]<br>D[31:24] | BE[2]<br>D[23:16] | BE[1]<br>D[15:08] | BE[0]<br>D[07:00] |

|------------|-------|-------|-------|-------------------|-------------------|-------------------|-------------------|

| 64-bit     | No    | No    | No    | Yes               | Yes               | Yes               | Yes               |

| 32-bit     | Yes   | No    | No    | Yes               | Yes               | Yes               | Yes               |

| 16-bit     | Yes   | Yes   | No    | No                | No                | Yes               | Yes               |

| 8-bit      | Yes   | Yes   | Yes   | No                | No                | No                | Yes*2             |

<sup>\*1 &</sup>quot;Yes" means the signal is used for control and "No" means the signal is not used.

Table 1-3: Relations between Address and Byte Enable

#### (7) Sequential and continuous access

The *Buffer Data Port* register shall be accessed by sequential and continuous manner. The buffer pointer is controlled by the Byte Enable patterns when accessing to the Buffer Data Port register. Therefore, Byte Enable patterns shall be sequential and continuous as well. The order of Byte Enable is according to little endian format. For example, *BE*[1] is accessed, next access shall start form *BE*[2]. Random or skipped access is not allowed.

Table 1-4 shows possible byte enables patterns that shall be supported by the Host Controller. However, if the system controller supports write merge, it may generate the other byte enable patterns. To avoid generating unsupported byte enable patterns for the 32-bit or 64-bit bus

<sup>\*2:</sup> BE[00] for 8-bit bus is always 1 therefore it may not be defined.

system, the Host Driver is allowed to use word or double word access to the *Buffer Data Port* register except for the last access to every block data.

| OK     | BE[3:0]=0011b (2-byte) => | BE[3:0]=1100b (2-byte) => | BE[3:0]=0011b (2-byte)    |

|--------|---------------------------|---------------------------|---------------------------|

| OK     | BE[3:0]=1100b (2-byte) => | BE[3:0]=1111b (4-byte) => | BE[3:0]=0011b (2-byte)    |

| OK     | BE[3:0]=1111b (4-byte) => | BE[3:0]=1111b (4-byte) => | BE[3:0]=1111b (4-byte)    |

| Not OK | BE[3:0]=0011b (2-byte) => | BE[3:0]=0011b (2-byte)    | (Cannot skip BE[2],BE[3]) |

| Not OK | BE[3:0]=0011b (2-byte) => | BE[3:0]=1111b (4-byte)    | (Cannot skip BE[2],BE[3]) |

| Byte Enable |        | BE[3]    | BE[2]    | BE[1]    | BE[0]    |

|-------------|--------|----------|----------|----------|----------|

| Data Bus    | }      | D[31:24] | D[23:16] | D[15:08] | D[07:00] |

| Access      | 4-byte | 1        | 1        | 1        | 1        |

| Type        | 2-byte | 0        | 0        | 1        | 1        |

|             | 2-byte | 1        | 1        | 0        | 0        |

|             | 1-byte | 0        | 0        | 0        | 1        |

|             | 1-byte | 0        | 0        | 1        | 0        |

|             | 1-byte | 0        | 1        | 0        | 0        |

|             | 1-byte | 1        | 0        | 0        | 0        |

<sup>\* 1</sup> means BE is valid and 0 means BE is not valid.

Table 1-4: Available Byte Enable Pattern for Buffer Data Port Register

#### (8) Buffer Control with Block Size

The buffer preserves data up to the block size specified by the *Block Size* register. Following definitions of controlling buffer enable the Host Driver to access the *Buffer Data Port* register repeatedly with 32-bit width regardless of block size.

In case of write operation, the buffer accumulates the data written through the *Buffer Data Port* register. When the buffer pointer reaches the block size, **Buffer Write Enable** in the *Present State* register changes 1 to 0. It means no more data can be written to the buffer. Excess data of the last write is ignored. For example, if just lower 2 bytes data can be written to the buffer and a 32-bit (4-byte) block of data is written to the *Buffer Data Port* register, the lower 2 bytes of data is written to the buffer and the upper 2 bytes is ignored. Every time **Buffer Write Enable** changes 0 to 1, it means a next block of data can be written to the buffer. A new blocks write shall always start from BE[00] position. After that, a block of data can be written to the buffer without checking **Buffer Write Enable**.

In case of read operation, every time **Buffer Read Enable** in the *Present State* register changes 0 to 1, a block of data can be read through the *Buffer Data Port* register. A new block read shall always start from BE[00] position. After that, a block of data can be read from the buffer without checking **Buffer Read Enable**. Excess data of the last read is ignored. For example, if just lower 2 bytes of data are left in the buffer and a 32-bit (4-byte) read is performed, the lower 2 bytes is valid but the upper 2 bytes is undefined. When the buffer pointer reaches block size, **Buffer Read Enable** changes 1 to 0. It means no more data can be read from the buffer.

#### Implementation Note:

Table 1-4 implies that the Host Driver should align register accesses on address boundaries matching the number of bytes in the access. That is, single byte accesses may be aligned on any offset within the register set; word (double byte) accesses should be aligned on two-byte offsets; and double-word (quad byte) accesses should be aligned on four-byte offsets. According to the feature (3), the Host Driver can always access *Buffer Data Port* register with double-word access.

#### 1.7.2 Determining Buffer Block Length

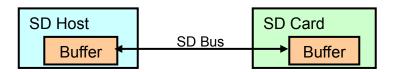

Figure 1-5: Buffer Size Relation between Host and Card

To be able to transfer blocks of data at a burst, the relationship between Host Controller and SD card buffer sizes is important. The Host Driver shall use the same buffer size for both Host Controller and SD Card. The buffer size is determined by block size. If the maximum block size of Host Controller and SD Card is different (capability), the Host Driver shall use the smaller one as the maximum block size of block size register. The maximum Host Controller buffer size is defined by the **Max Block Length** field in the *Capabilities* register in SD mode and the **Host Maximum Block Length** field in the *UHS-II LINK/TRAN Capabilities* register.

#### Implementation Note:

The card buffer size is described as maximum block length in the Card Specific Data (CSD) register for memory cards (READ\_BL\_LEN and WRITE\_BL\_LEN) and in the CCCR (Function 0) and FBR (Function 1-7) for SDIO cards. The Physical Layer Specification re-defines that the maximum block length is only used to calculate capacity of memory card. Even though it indicates larger than 512 bytes, block length shall be set to 512 byte for data transfer. This is because 512 bytes block length is required to keep compatibility with 512 bytes data boundary.

The Host Controller shall have at least 512 bytes buffer and 512 bytes fixed block length is used for memory data transfer. UHS-II has a parameter of N\_FCU, which indicates the number of blocks per flow control unit. Host Controller requires at least 512 bytes \* N\_FCU buffer size. In case of SDIO, buffer size is variable up to the maximum block length. If multiple functions SDIO card has different buffer size in each function, Card Driver should adjust buffer size depends on the maximum block length of each function.

#### 1.7.3 Dividing Large Data Transfer

On transferring very large data, Card Driver should divide the data into small unit for avoiding an operation continues to hold SD Bus Interface long time. Small data unit access allows time-sharing operation and several applications may use a common SD Card at the same time.

Following the Speed Class write conditions (defined by the Physical Layer Specification) is the most efficient method to write data to SD Memory card.

Data transfer size of CMD53 is limited by the 9-bit block count field in the argument. Up to 511 blocks can be transferred per this command.

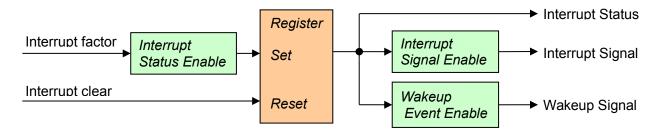

## 1.8 Relationship between Interrupt Control Registers

The Host Controller implements a number of interrupt sources. Interrupt sources can be enabled as interrupts or as system wakeup signals as shown in Figure 1-6. If the interrupt source's corresponding bit in the *Normal Interrupt Status Enable* or *Error Interrupt Status Enable* register is 1 and the interrupt becomes active, its active state is latched and made available to the Host Driver in the *Normal Interrupt Status* register or the *Error Interrupt Status* register. Interrupt Status shall be cleared when *Interrupt Status Enable* is cleared. (This is not expressed in the Figure 1-6.)

An interrupt source with its bit set in an interrupt status register shall assert a system interrupt signal if its corresponding bit is also set in the *Normal Interrupt Signal Enable* register or the *Error Interrupt Signal Enable* register. Once signaled, most interrupts are cleared by writing a 1 to the associated bit in the interrupt status register. Card interrupts, however, shall be cleared by the Card Driver. If the Card Interrupt is generated, the Host Driver may clear Card Interrupt Status Enable to disable card interrupts while the Card Driver is processing them. After all interrupt sources are cleared, the Host Driver sets it again to enable another card interrupt. Disabling the Card Interrupt Status Enable avoids generating multiple interrupts during processing interrupt service.

The Wakeup Control register enables Card Interrupt, Card Insertion, or Card Removal status changes to be configured to generate a system wakeup signal. These interrupts are enabled or masked independently of the Normal Interrupt Signal Enable register. The kind of wakeup event can be read from the Normal Interrupt Status register.

The interrupt signal and wakeup signal are logical ORed and shall be read from the *Slot Interrupt Status* register.

#### Implementation Note:

The Host Driver is responsible for enabling wakeup signals and disabling interrupt signals when the Host System goes into its sleep mode, and for disabling wakeup signals and enabling interrupt signals when the Host System goes into run mode. The Host Driver should not enable both at the same time.

#### Implementation Note:

The Host Systems may implement interrupt and wakeup signals in various ways. For example, the PCI bus supports **PME#**, which can be asserted without PCI clock, then interrupts use **INTx#** and wakeups use **PME#**. Alternatively, the system may use an ORed signal of interrupt and wakeup if the system bus supports one interrupt line to the Host Controller.

Figure 1-6: Logical Relation for Interrupt Registers

| Interrupt<br>Status Enable | Interrupt<br>Signal Enable | Wakeup<br>Event Enable | Interrupt Status | Interrupt Signal |

|----------------------------|----------------------------|------------------------|------------------|------------------|

| 0 (Mask)                   | x (don't care)             | x (don't care)         | 0 (Not exist)    | 0 (De-assert)    |

| 1 (Enable)                 | 0 (Mask)                   | x (don't care)         | x (don't care)   | 0 (De-assert)    |

| 1 (Enable)                 | 1 (Enable)                 | x (don't care)         | 0 (Not exist)    | 0 (De-assert)    |

| 1 (Enable)                 | 1 (Enable)                 | x (don't care)         | 1 (Exist)        | 1 (Assert)       |

Table 1-5 : Interrupt Signal Table

| Interrupt<br>Status Enable | Interrupt<br>Signal Enable | Wakeup<br>Event Enable | Interrupt Status | Wakeup Signal |

|----------------------------|----------------------------|------------------------|------------------|---------------|

| 0 (Mask)                   | x (don't care)             | x (don't care)         | 0 (Not exist)    | 0 (De-assert) |

| 1 (Enable)                 | x (don't care)             | 0 (Mask)               | x (don't care)   | 0 (De-assert) |

| 1 (Enable)                 | x (don't care)             | 1 (Enable)             | 0 (Not exist)    | 0 (De-assert) |

| 1 (Enable)                 | x (don't care)             | 1 (Enable)             | 1 (Exist)        | 1 (Assert)    |

Table 1-6: Wakeup Signal Table

Implementation Note: The Host Controller may implement asserted wakeup or interrupt signals as active high or active low.

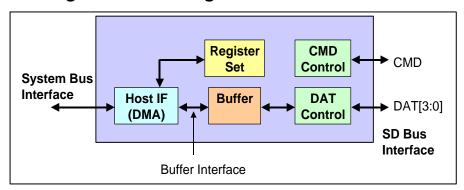

## 1.9 HW Block Diagram and Timing Part

Figure 1-7 : Block Diagram of Host Controller

The Host Controller has two bus interfaces, the System Bus Interface and the SD Bus Interface. The Host Controller assumes that these interfaces are asynchronous (that is, are working on different clock frequencies). The Host Driver is on system bus time (because it is software executed by the Host Controller CPU, on its system clock). The SD card is on SD Bus time (that is, its operation is synchronized by **SDCLK**). The Host Controller shall synchronize signals to communicate between these interfaces. Blocks of data shall be synchronized at the buffer module. All status registers shall be synchronized by the system clock and maintain synchronization during output to the system interface. Control registers, which trigger SD Bus transactions, shall be synchronized by **SDCLK**. Therefore, there will be a timing delay when propagating signals between the two interfaces. This means the Host Driver cannot do real time control of the SD Bus and needs to rely on the Host Controller to control the SD Bus according to register settings.

The Buffer Interface enables internal read and write buffers (Refer to use of the **Buffer Read Enable** and **Buffer Write Enable** in the *Present State* register as described in Section 1.7 "Buffer Control"). The **Transfer Complete** interrupt status indicates completion of the read / writes transfer for both DMA and non-DMA transfers. However, the timing of data transfer completion is different between reads and writes. Read transfers shall be completed after all valid data have been transferred to the Host System and are ready for the Host Driver to access. Write transfers shall be completed after all valid data have been transferred to the SD card and the busy state is over. If all block data is written to buffer, Host Driver should ignore another Buffer Write Ready until Transfer Complete is generated.

Table 1-7 shows the relation between statuses and interrupts for data transfer.

| Type of Data transfer    | Buffer Status       | Buffer Interrupt   | Complete Interrupt |

|--------------------------|---------------------|--------------------|--------------------|

| Write Transfer (Non DMA) | Buffer Write Enable | Buffer Write Ready | Transfer Complete  |

| Write Transfer (DMA)     | (Driver ignores)    | (Driver ignores)   | Transfer Complete  |

| Read Transfer (Non DMA)  | Buffer Read Enable  | Buffer Read Ready  | Transfer Complete  |

| Read Transfer (DMA)      | (Driver ignores)    | (Driver ignores)   | Transfer Complete  |

Table 1-7: Summary of Register Status for Data Transfer

#### 1.10 Power State Definition of SD Host Controller

Implementation Note: Table 1-8 defines controller power states, which are listed in increasing order of power consumption. The Host Controller should reduce the power consumption by using these conditions.

| SD<br>Card | Internal<br>Clock *1 | SD Power | SD Clock  | SD Bus | Power<br>State *2 | Comment                   |

|------------|----------------------|----------|-----------|--------|-------------------|---------------------------|

| Caru       |                      |          |           |        | State 2           |                           |

|            | Stop                 | OFF      | Stop      | -      | P00               | Host not used             |

| No exist   | Oscillate            | OFF      | Stop      | -      | P01               | No card                   |

| INO EXIST  | Oscillate            | ON       | Stop      | -      | P02               | Short transition state *3 |

|            | Oscillate            | ON       | Oscillate | -      | P03               | Short transition state *3 |